Maintenance Manual

# Model 810 Printer

994386-0001, Rev. J May 1984

Volume I

# TEXAS INSTRUMENTS

### Copyright © 1984 Texas Instruments Incorporated All Rights Reserved — Printed in USA

The information herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques or apparatus described herein are the exclusive property of Texas Instruments Incorporated.

No copies of the information or drawings shall be made without the prior consent of Texas Instruments Incorporated.

INSERT LATEST CHANGED PAGES, DESTROY SUPERSEDED PAGES

### LIST OF EFFECTIVE PAGES

Model 810 Printer Maintenance Manual, Vol. I Part No. 994386-0001 Original Issue: 15 July 1977 Revision J: May 1984

Total number of pages in this publicaties is **278** consisting of the following:

| Page<br>No.               | Change<br>No. | Page<br>No.           | Change<br>No. | Page<br>No.    | Change<br>No. |

|---------------------------|---------------|-----------------------|---------------|----------------|---------------|

| Front Cover               | 0             | B-1                   | 0             | Business Reply | 0             |

| Effective Pages           | 0             | C-1 – C-5             | 0             | Back Cover     | 0             |

| iii —x                    | 0             | D-1 – D-21            | 0             |                | -             |

| 1-1 - 1-4                 | 0             | E-1 — E-16            | 0             |                |               |

| 2-1 -2-6                  | 0             | F-1 — F-43            | 0             |                |               |

| <b>3-1</b> - <b>3</b> -10 | 0             | G-1 —G-8              | 0             |                |               |

| 4-1 -4-8                  | 0             | H-1                   | 0             |                |               |

| 5-1 - 5-7                 | 0             | I-1 —I-2              | 0             |                |               |

| 6-1 —6-6                  | 0             | J-1 — J-3             | 0             |                |               |

| 7-1 – 7-43                | 0             | К-1 — К-32            | 0             |                |               |

| 8-1 -8-28                 | 0             | L-1 — L-9             | 0             |                |               |

| A-1 — A-10                | 0             | User's Response Sheet | 0             |                |               |

| Revision Date |                                                                                        | ECN                                                                                                                                                                                                                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                    |  |

|---------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|               | Number                                                                                 | Level                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                |  |

| 3/15/78       | 432918                                                                                 | D                                                                                                                                                                                                                                                                                | Update per ECN                                                                                                                                                                                                                                                                                                                                                                 |  |

| 6/1/78        | 432332                                                                                 | D                                                                                                                                                                                                                                                                                | Update per ECN                                                                                                                                                                                                                                                                                                                                                                 |  |

| 10/9/78       | 439638                                                                                 | D                                                                                                                                                                                                                                                                                | Update per ECN                                                                                                                                                                                                                                                                                                                                                                 |  |

| 11/15/79      | 444060                                                                                 | E                                                                                                                                                                                                                                                                                | Update per ECN                                                                                                                                                                                                                                                                                                                                                                 |  |

| 10/10/80      | 469070                                                                                 | D                                                                                                                                                                                                                                                                                | Update per ECN                                                                                                                                                                                                                                                                                                                                                                 |  |

| 9/22/81       | 443519                                                                                 | D                                                                                                                                                                                                                                                                                | Update per ECN                                                                                                                                                                                                                                                                                                                                                                 |  |

| 10/28/81      | 492910                                                                                 | Е                                                                                                                                                                                                                                                                                | Update per ECN                                                                                                                                                                                                                                                                                                                                                                 |  |

| 4/16/82       | 443532                                                                                 | D                                                                                                                                                                                                                                                                                | Update per ECN                                                                                                                                                                                                                                                                                                                                                                 |  |

| 5/1/84        | 498658                                                                                 | Ε                                                                                                                                                                                                                                                                                | Update per ECN; incorporate into two volumes                                                                                                                                                                                                                                                                                                                                   |  |

|               |                                                                                        |                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                |  |

|               | 3/15/78<br>6/1/78<br>10/9/78<br>11/15/79<br>10/10/80<br>9/22/81<br>10/28/81<br>4/16/82 | Number           3/15/78         432918           6/1/78         432332           10/9/78         439638           11/15/79         444060           10/10/80         469070           9/22/81         443519           10/28/81         492910           4/16/82         443532 | Number         Level           3/15/78         432918         D           6/1/78         432332         D           10/9/78         439638         D           11/15/79         444060         E           10/10/80         469070         D           9/22/81         443519         D           10/28/81         492910         E           4/16/82         443532         D |  |

Address all correspondence regarding orders to:

Texas Instruments Incorporated Data Systems Group P.O. Box 1444, M/S 7793 Houston, TX 77251

# Preface

The *Model 810 Printer Maintenance Manual* consists of two volumes.

Volume I, this volume, provides detailed information for installing, operating, maintaining, and replacing assemblies and subassemblies of the Texas Instruments OMNI 800\* Model 810 printer in Sections 1 through 8 and the Appendixes.

Volume II provides drawings, lists of materials, schematics, and logic diagrams in Sections 9 and 10.

**SECTION 1. GENERAL DESCRIPTION** — Provides a description of the Model 810 printer and lists the features and specifications.

**SECTION 2. INSTALLATION** — Specifies space and power requirements and provides step by step instructions for setting up the printer after it is unpacked.

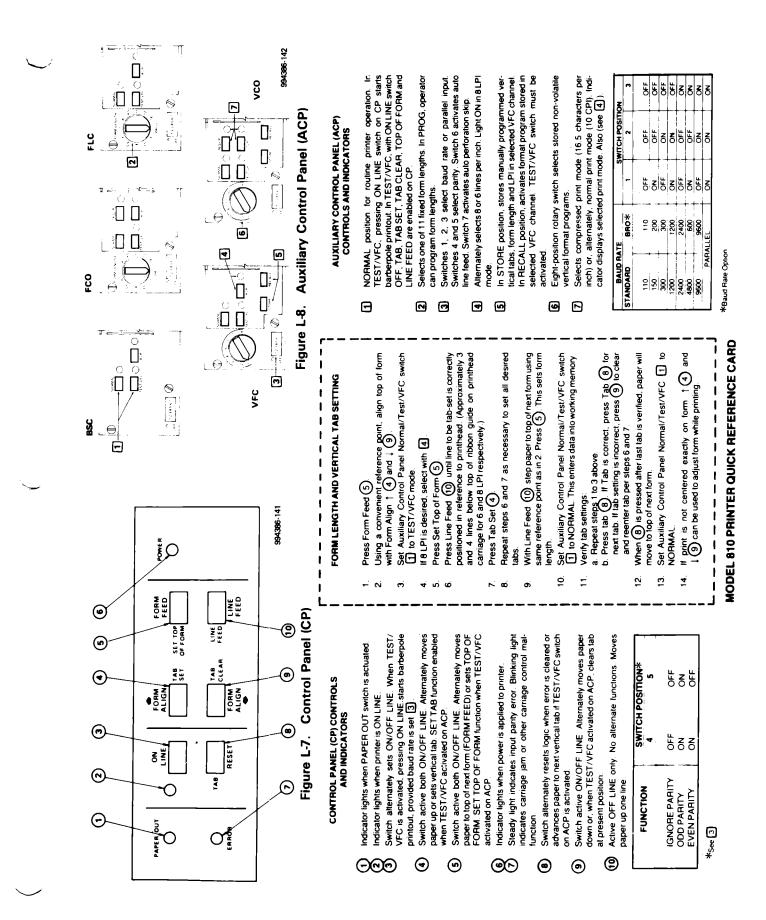

**SECTION 3. OPERATING INSTRUCTIONS** (Manual Control) — Describes all control and indicator actions and lists specific operating procedures.

**SECTION 4. OPERATING INSTRUCTIONS (Software Control)** — Provides the programming material required to operate the printer through the communication line, with and without the line buffer option.

**SECTION 5. INTERFACE INFORMATION** (**Printers Without Line Buffer Option**) — Presents interface data such as signal criteria, cabling, and grounding connections for printers without the line buffer option.

\*Trademark of Texas Instruments Incorporated.

**SECTION 6. INTERFACE INFORMATION** (**Printers With Line Buffer Option**) — Provides interface data for printers equipped with the line buffer option.

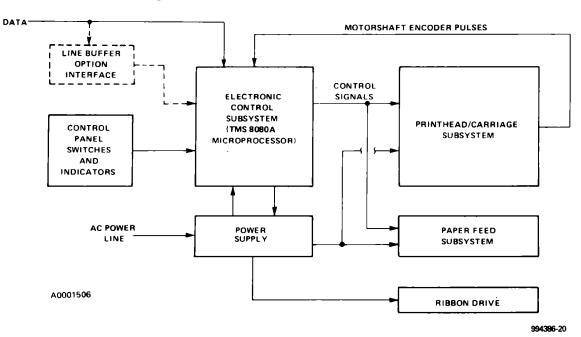

**SECTION 7. THEORY OF OPERATION** – Contains the theory of operation including a system block diagram, a discussion of dot matrix printing, and an overview of the major printer subsystems.

**SECTION 8. MAINTENANCE** — Discusses recommended procedures for routine and preventive maintenance.

SECTION 9. ASSEMBLY DRAWINGS AND PARTS LISTS (Volume II) — Contains all engineering drawings and parts lists for the Model 810 printer.

**SECTION 10. SCHEMATIC DIAGRAMS** (Volume II) — Provides the logic diagrams and schematics for the printer.

**APPENDIXES** — Contain information useful for reference. Subjects covered are:

- A Dot Matrix Character Generation

- B ASCII Control and Character Codes

- C Model 810 Printer Versions, Options, and Accessories

- D TMS 8080A Microprocessor

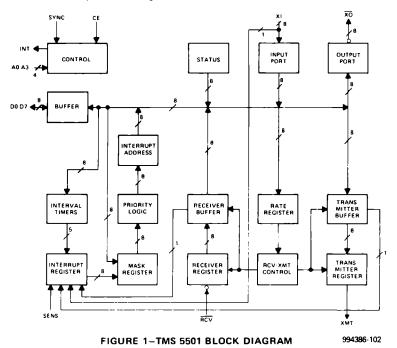

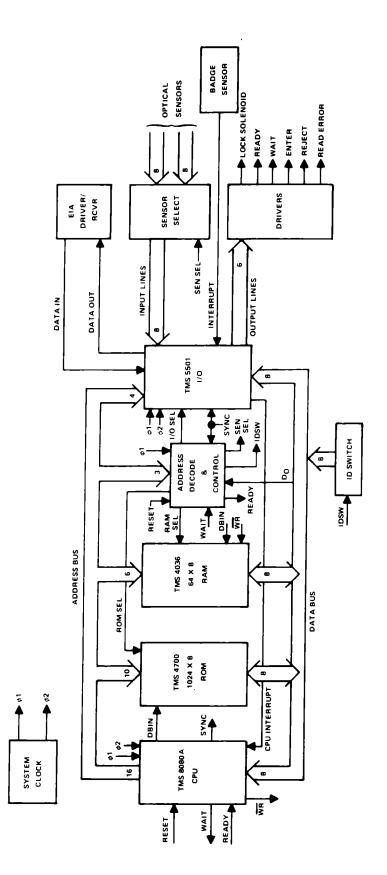

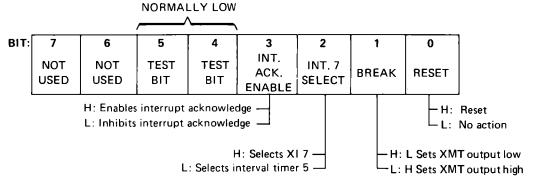

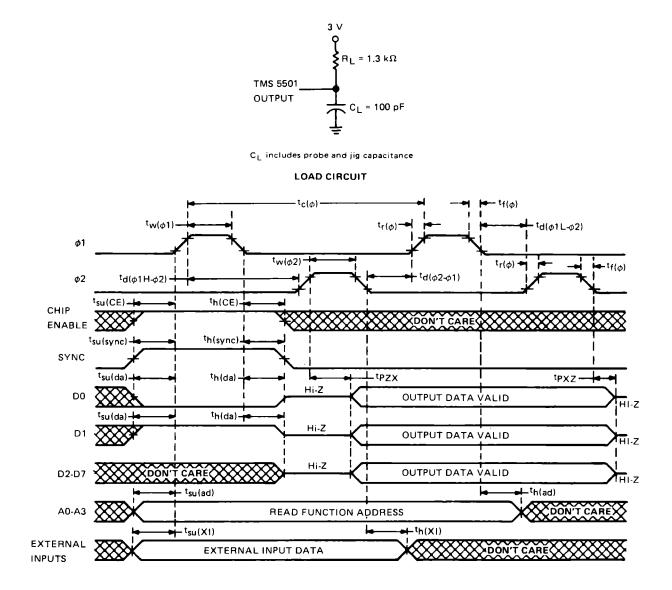

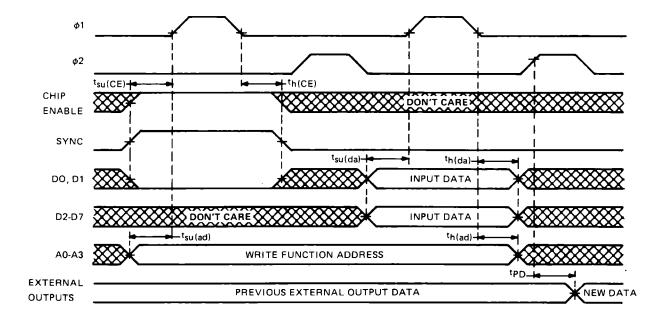

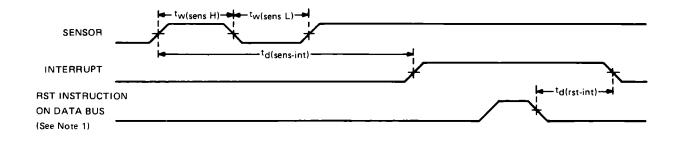

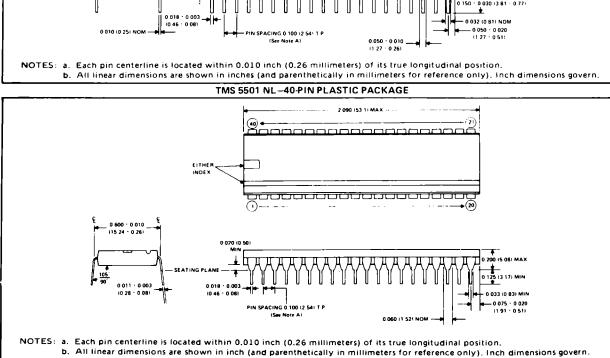

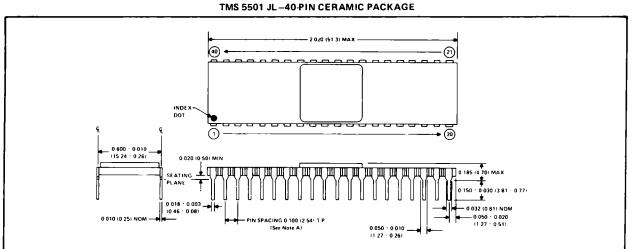

- E TMS 5501 I/O Controller

- F Installation of Option Kits

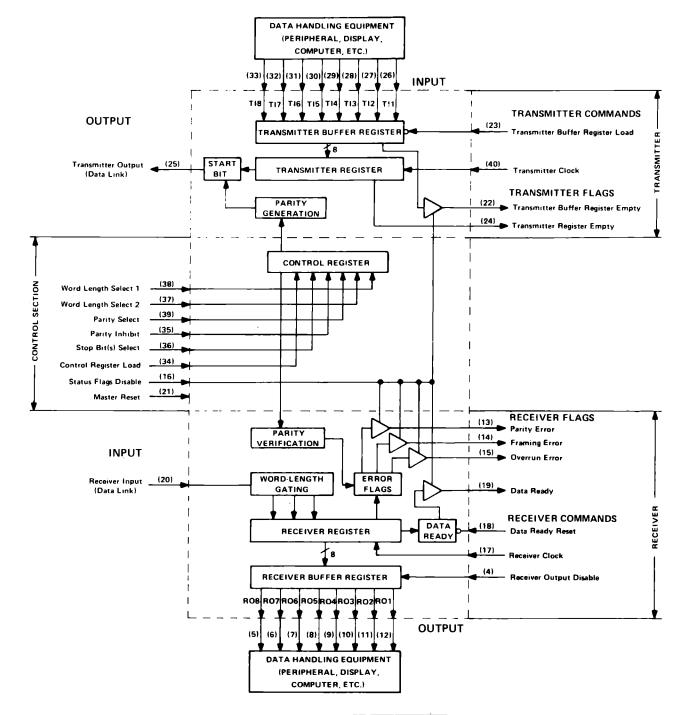

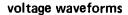

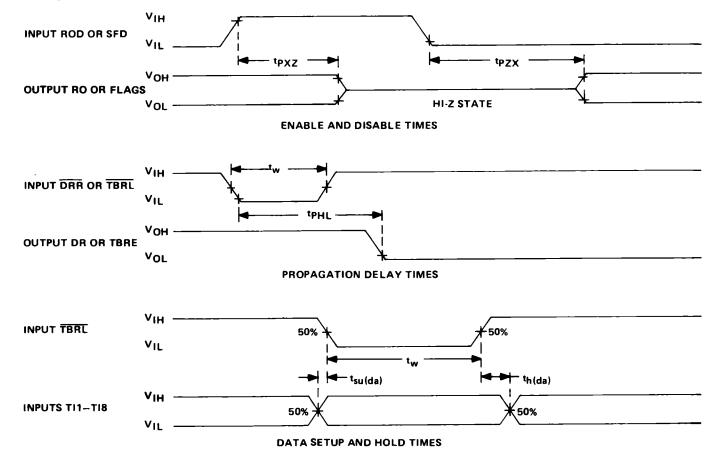

- G TMS 6011 Data Sheets

- H Cable Pin Assignments

- I U.S. ASCII/Katakana Dual Character Set

- J Strappable Options for Processor and Line Buffer Boards

- K Theory of Operation for Drive Board (TI Part No. 994322) and Power Supply (TI Part No. 994394)

- L First-Generation Front Panels and Carriage Motor Assembly

The various options for the Model 810 printer are identified throughout this manual by configuration codes. For example, BSC indicates the basic printer. Options installed on the Model 810 printer can be determined by examining the printer configuration label on the underside of the access door for comparison to codes listed in Appendix C.

### **OTHER PUBLICATIONS**

The following additional publications support the Model 810 printer.

- Model 810 Printer Operator's Manual (TI Part No. 994353-9701)

- Model 810 Maintenance Manual Volume II (TI Part No. 994386-0002)

To order copies, send a company purchase request to:

Texas Instruments Incorporated Terminal Spare Parts — M/S 7793 P. O. Box 1444 Houston, Texas 77251

iv

# **Table of Contents**

| Section | Title                                      | Page  |

|---------|--------------------------------------------|-------|

|         | Preface                                    | iii   |

| 1       | General Description                        |       |

| 1.1     | Standard Features                          | . 1-1 |

| 1.2     | Configurations                             | . 1-2 |

| 1.3     | Specifications                             | . 1-2 |

| 1.4     | Modifiable Features                        | . 1-3 |

| 1.5     | Optional Features                          | . 1-3 |

| 1.6     | Accessories                                | . 1-3 |

| 2       | Installation                               |       |

| 2.1     | Introduction                               |       |

| 2.2     | Space Requirements                         | . 2-1 |

| 2.3     | Unpacking and Setting Up                   | . 2-1 |

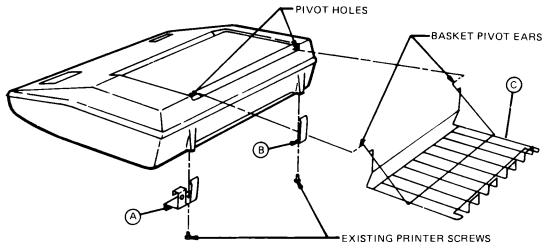

| 2.4     | Paper Basket Installation                  | . 2-2 |

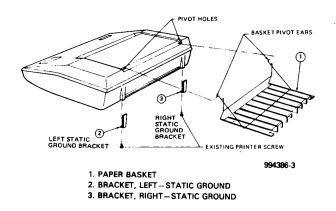

| 2.4.1   | Terminal Paper Basket                      | . 2-2 |

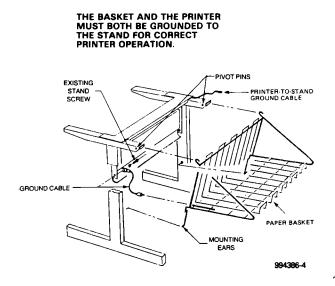

| 2.4.2   | Terminal Stand Paper Basket                |       |

| 2.5     | Connecting Power                           |       |

| 2.5.1   | Grounding Requirements                     |       |

| 2.5.2   | Line Voltage Selection                     |       |

| 2.6     | Ribbon Installation                        |       |

| 2.7     | Paper Loading                              | . 2-5 |

| 3       | Operating Instructions<br>(Manual Control) |       |

| 3.1     | Introduction                               | . 3-1 |

| 3.2     | Operator Controls and                      |       |

|         | Indicators                                 |       |

| 3.2.1   | PAPER-OUT Indicator                        |       |

| 3.2.2   | ERROR Indicator                            | . 3-1 |

| 3.2.3   | ONLINE Switch and                          |       |

|         | Indicator                                  |       |

| 3.2.4   | RESET/TAB Switch                           | . 3-2 |

| 3.2.5   | FORM ALIGN/TAB SET                         |       |

|         | Switch                                     | 3-2   |

.

| Section | Title                                                       | Page                |

|---------|-------------------------------------------------------------|---------------------|

| 3.2.6   | FORM ALIGN/TAB CLEAR<br>Switch                              | 3-2                 |

| 3.2.7   | FORM FEED/SET TOP OF FORM                                   | 1                   |

| 3.2.8   | Switch                                                      |                     |

| 3.2.9   | Switch                                                      |                     |

| 3.2.9   | Auxiliary Controls and                                      | . <b>J-</b> Z       |

| 3.3     | Indicators                                                  | 3-2                 |

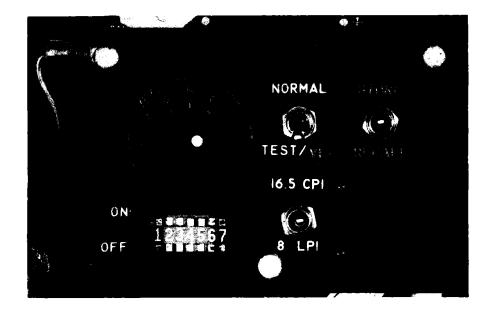

| 3.3.1   | NORMAL and TEST/VFC                                         | . 0-2               |

| 0.0.1   | Switches                                                    | . 3-3               |

| 3.3.2   | PENCIL Switches                                             |                     |

| 3.3.3   | 8 LPI Switch/Indicator                                      | . 3-3               |

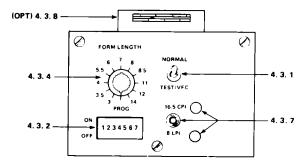

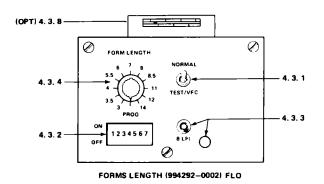

| 3.3.4   | FORM LENGTH Rotary Switch (Fi<br>and FCO Printers Only)     | LC<br>. <b>3</b> -3 |

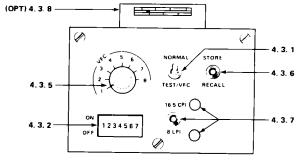

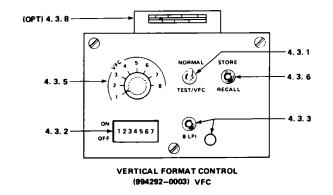

| 3.3.5   | VFC Switch (VFC and VCO Printe Only)                        | rs                  |

| 3.3.6   | STORE and RECALL Switches (VF<br>and VCO Printers Only)     | -C                  |

| 3.3.7   | 16.5 CPI Switch and Indicator (VF<br>and VCO Printers Only) | С                   |

| 3.4     | Operating Procedures                                        |                     |

| 3.4.1   | Power-up Procedure                                          | •                   |

|         | (All Printers)                                              | 3-4                 |

| 3.4.2   | Top-of-Form Adjustment<br>(All Printers)                    |                     |

| 3.4.3   | Printhead Adjustment                                        | 0-0                 |

|         | (All Printers)                                              | 3-5                 |

| 3.4.4   | Self-Test Diagnostic                                        |                     |

| 3.4.5   | Lines-per-Inch Spacing<br>(All Printers)                    |                     |

| 3.4.6   | Characters-per-Inch Spacing<br>(FCO, VCO)                   |                     |

| 3.4.7   | Baud Rate/Parallel Input<br>Selection (All Printers)        |                     |

| 3.4.8   | Parity Selection                                            |                     |

| 3.4.9   | (All Printers)                                              | J-/                 |

|         |                                                             |                     |

| Section      | Title                                             | Page        |

|--------------|---------------------------------------------------|-------------|

|              | Override                                          | 3-7         |

| 3.4.10       | Automatic Perforation                             |             |

| 3.4.11       | Skip Override                                     | 3-7         |

| 3.4.11       | (BSC)                                             | 3-7         |

| 3.4.12       | Vertical Tab Setting                              |             |

|              | (All Printers)                                    | 3-7         |

| 3.4.13       | Vertical Tab Clearing                             |             |

| 3.4.14       | (All Printers)<br>Fixed Form Length Selection     | 3-8         |

| 3.4.14       | (FCO, FLC)                                        | 3-8         |

| 3.4.15       | Programming Form Length                           |             |

|              | (All Printers)                                    | 3-8         |

| 3.4.16       | Storing Vertical Format                           |             |

| 3.4.17       | (VFC, FCO)                                        | 3-9         |

| 3.4.17       | Recalling Vertical Format<br>(VFC, VCO)           | 3-0         |

| 3.4.18       | Power-Down Procedures                             | 5-5         |

|              | (All Printers)                                    | 3-10        |

| 4            | Operating Instructions                            |             |

| -            | (Software Control)                                |             |

| 4.1          | Introduction                                      | <i>A</i> _1 |

| 4.1          | Commands (without Line                            |             |

|              | Buffer Option)                                    | . 4-1       |

| 4.3          | Commands (with Line                               |             |

|              | Buffer Option)                                    | . 4-1       |

| 4.4<br>4.4.1 | Software (Remote) Control<br>Software Form Length | . 4-6       |

| 4.4.1        | Setting                                           | 4-6         |

| 4.4.2        | Software Horizontal                               |             |

|              | Tab Setting                                       | . 4-6       |

| 4.4.3        | Software Line Width                               |             |

| 4.4.4        | Setting<br>Software Vertical Format               | . 4-6       |

| 4.4.4        | Recall                                            | . 4-7       |

| 4.4.5        | Software Vertical Format                          |             |

|              | Store                                             | . 4-7       |

| 4.4.6        | Software Vertical Tab                             | 47          |

| 4.4.7        | Setting<br>Software Expanded Print                | . 4-/       |

| 4.4./        | Setting                                           | . 4-8       |

|              |                                                   |             |

| 5            | Interface Information                             |             |

|              | (Printers without Line<br>Buffer Option)          |             |

|              |                                                   |             |

| 5.1          | Standard Interface                                |             |

| 5.2          | Cabling and Grounding                             |             |

| 5.3<br>5 2 1 | Serial Interface                                  |             |

| 5.3.1        | Baud Rate                                         | . ე-ქ       |

| Section | Title                              | Page     |

|---------|------------------------------------|----------|

| 5.3.2   | Signal Levels and                  |          |

|         | Terminations                       | . 5-3    |

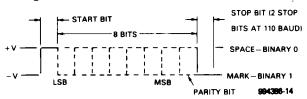

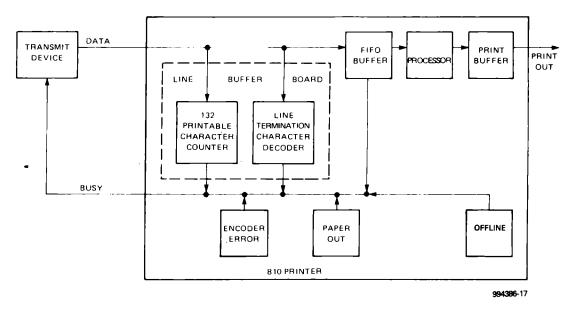

| 5.3.3   | Asynchronous Data Format           | . 5-3    |

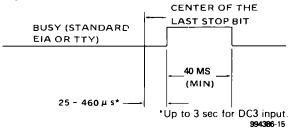

| 5.3.4   | Timing                             |          |

| 5.3.5   | Parity Checking                    |          |

| 5.4     | Parallel Interface (Optional)      |          |

| 5.4.1   | Signal Levels and                  |          |

|         | Terminations                       | . 5-4    |

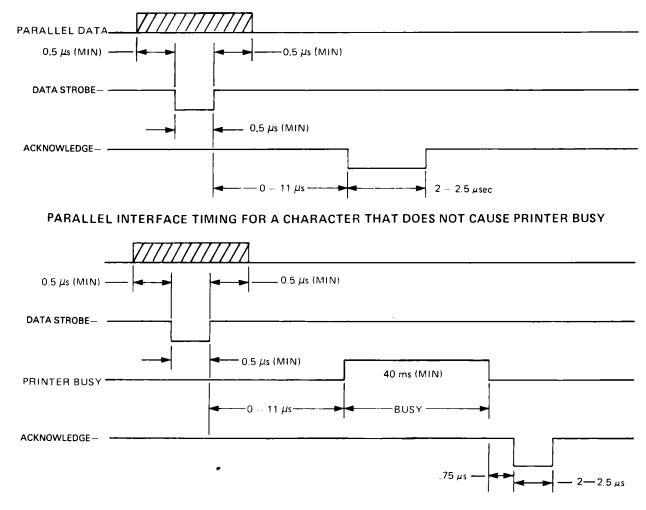

| 5.4.2   | Parallel Interface Timing          | . 5-5    |

| 5.4.3   | Data Strobe                        |          |

|         | Acknowledgement                    | . 5-5    |

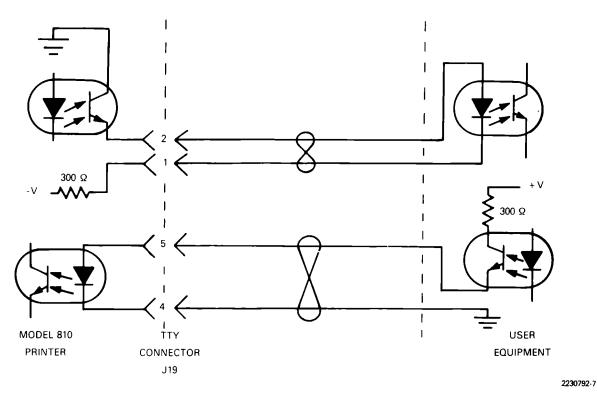

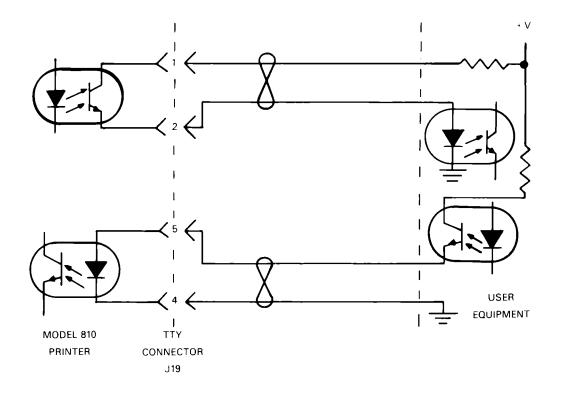

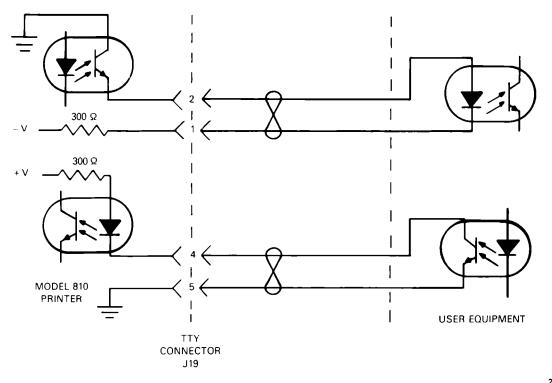

| 5.5     | TTY Current Loop Interface         |          |

|         | (Optional)                         | . 5-5    |

| 5.5.1   | Signal Levels and                  |          |

| ••••    | Terminations                       | . 5-6    |

| 5.5.2   | Basic TTY Interface                |          |

|         | Timing                             | . 5-6    |

| 5.6     | RS-422 Serial Interface (Optional) | . 5-6    |

| 5.7     | RS-422 Signal Convention           |          |

| 6       | Interface Information              |          |

| •       | (Printers with Line                |          |

|         | Buffer Option)                     |          |

|         | burier option,                     |          |

| 6.1     | Line Buffer Option                 |          |

|         | Interface                          | . 6-1    |

| 6.2     | Cabling and Grounding              |          |

| 6.3     | Serial Interface                   |          |

|         | (LBE Option)                       | . 6-2    |

| 6.3.1   | Baud Rate                          | . 6-2    |

| 6.3.2   | Signal Levels and                  |          |

|         | Terminations                       | . 6-3    |

| 6.3.3   | Asynchronous Data Format           |          |

| 6.4     | Parallel Interface                 |          |

|         | (LBP Option)                       | . 6-3    |

| 6.4.1   | Signal Levels and                  |          |

|         | Terminations                       | . 6-4    |

| 6.4.2   | Basic Parallel Timing              | . 6-4    |

| 6.4.3   | Data Strobe                        |          |

|         | Acknowledgment                     | . 6-5    |

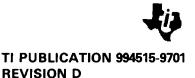

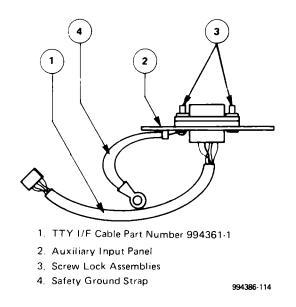

| 6.5     | TTY Current Loop Interface         |          |

|         | (LBT Option)                       | . 6-5    |

| 6.5.1   | Signal Levels and                  |          |

|         | Terminations                       | . 6-6    |

| 6.5.2   | Timing                             | . 6-6    |

| 7       | Theory of Operation                |          |

|         | ,p                                 |          |

| 7.1     | Introduction                       | 7-1      |

| 7.2     | Principles of Operation            |          |

| 7.2.1   | Electronic Control                 | · · · _~ |

|         | Subsystem                          | 7-2 🔍    |

ł

| Section | Ιπε                       | Page   |

|---------|---------------------------|--------|

| 7.2.2   | Printhead Carriage        |        |

|         | Subsystem                 | . 7-3  |

| 7.2.3   | Paper Feed Subsystem      | . 7-8  |

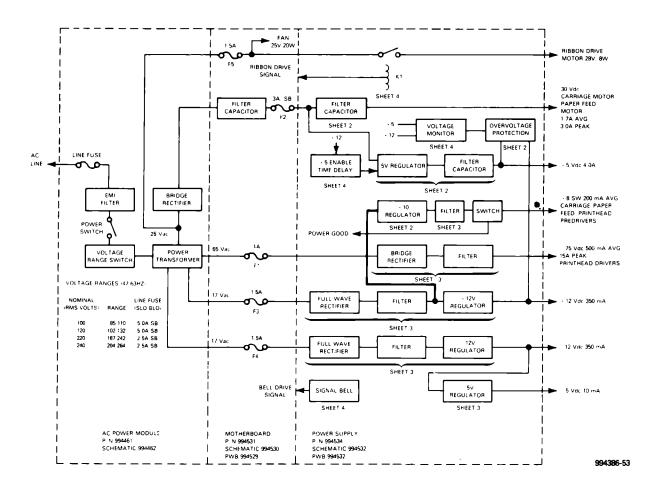

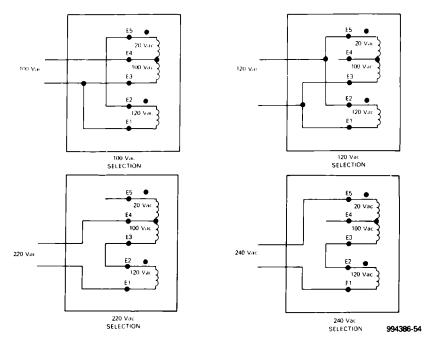

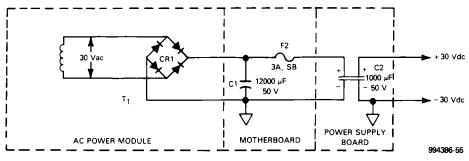

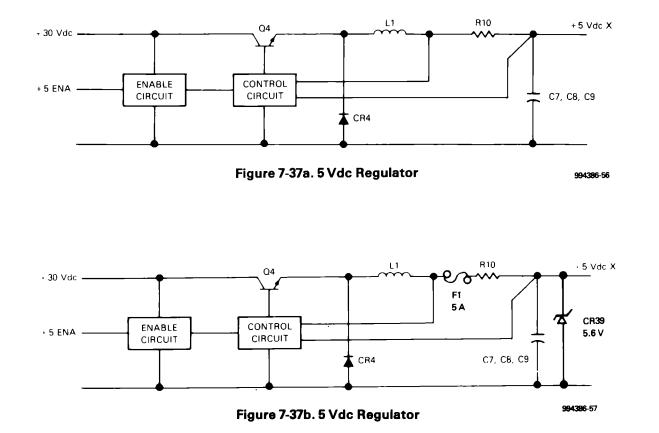

| 7.2.4   | Power Supply              | . 7-9  |

| 7.2.5   | Line Buffer Option        |        |

|         | Interface                 | . 7-10 |

| 7.3     | Theory of Operation       |        |

| 7.3.1   | Overview                  | 7-11   |

| 7.3.2   | Processor Board           |        |

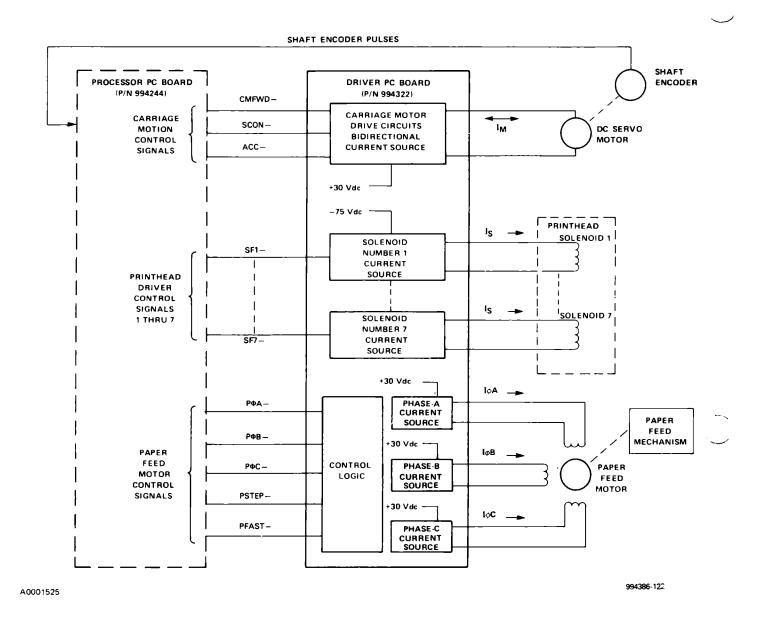

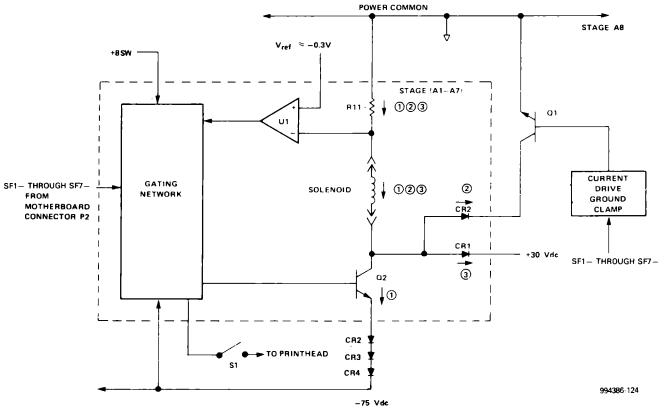

| 7.3.3   | Driver Board              | 7-22   |

| 7.3.4   | Power Supply              | 7-34   |

| 7.3.5   | Current Loop Option       |        |

|         | Board                     | 7-40   |

| 7.3.6   | Line Buffer Option        |        |

|         | Board                     | 7-41   |

| 8       | Maintenance               |        |

| 8.1     | Introduction              | 8-1    |

| 8.2     | Preventive Maintenance    |        |

| 8.3     | Lubrication and Cleaning  |        |

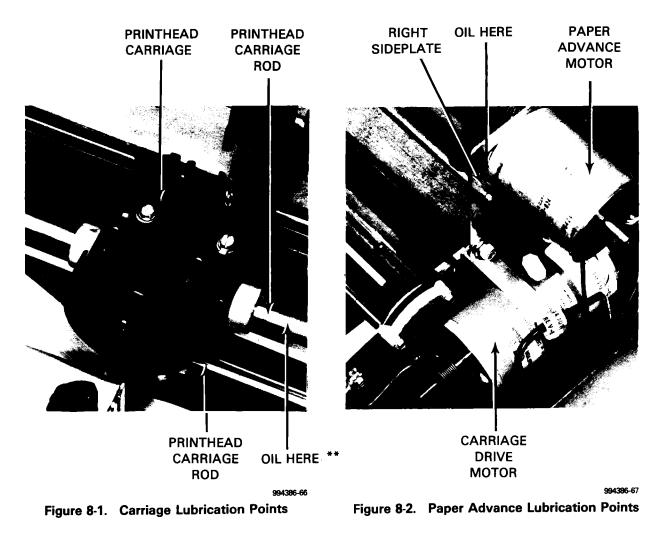

| 8.3.1   | Oiling Printer Carriage   |        |

| 0.0.1   | Guide Rods                | 8-2    |

| 8.3.2   | Oiling Paper Advance Gear |        |

| ••••    | Eyelet                    | 8-2    |

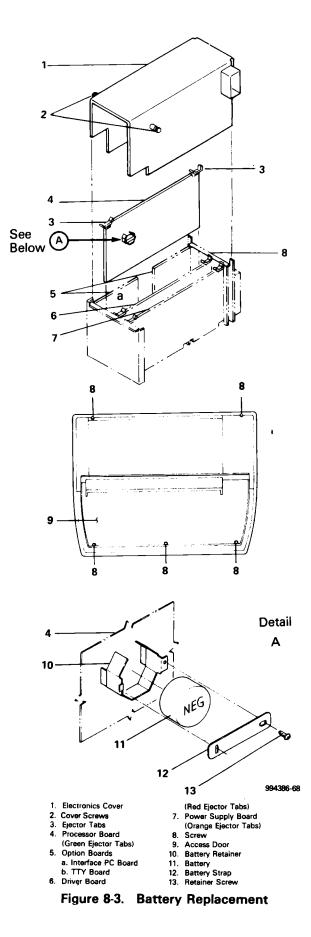

| 8.4     | Battery Replacement       | 8-3    |

| 8.5     | Routine Maintenance and   |        |

|         | Adjustments               | 8-4    |

| 8.5.1   | Ribbon Guide Adjustment   |        |

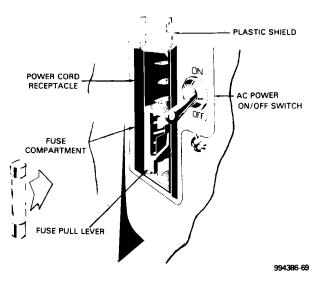

| 8.5.2   | Fuse Replacement          |        |

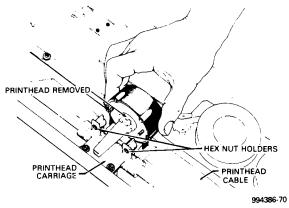

| 8.5.3   | Printhead Replacement     | 8-5    |

| 8.6     | Troubleshooting           | 8-5    |

| 8.7     | Removal and Replacement   | 8-7    |

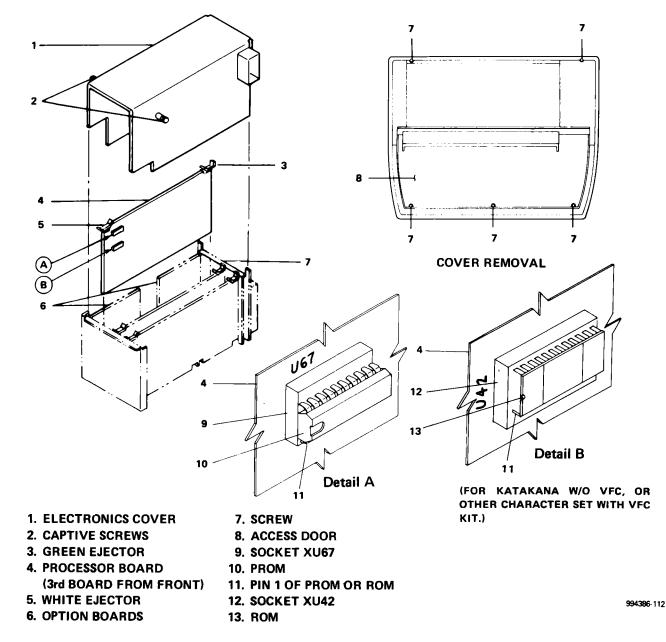

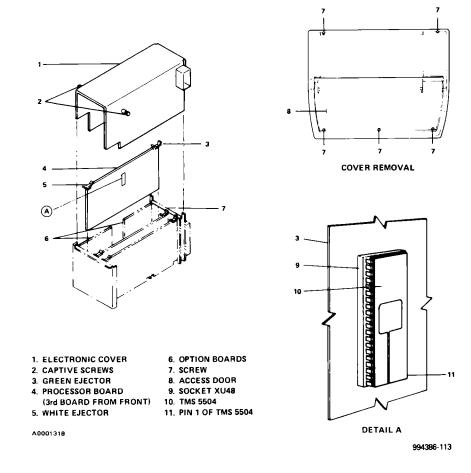

| 8.7.1   | Printed Circuit Board(s)  | 8-7    |

| 8.7.2   | AC Power Module Removal   |        |

|         | and Replacement           |        |

| 8.7.3   | Motherboard               |        |

| 8.7.4   | Fan Assembly              | 8-11   |

| 8.7.5   | Paper Drive Motor         |        |

|         | Assembly                  | 8-12   |

| Section | Title F                              | <b>Page</b> |

|---------|--------------------------------------|-------------|

| 8.7.6   | Paper Tractor                        | 8-14        |

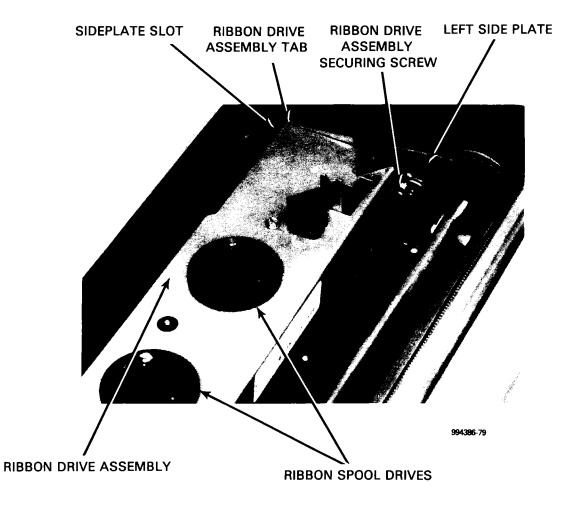

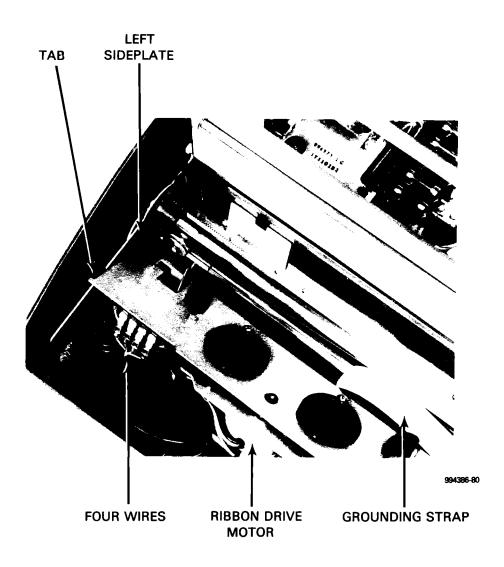

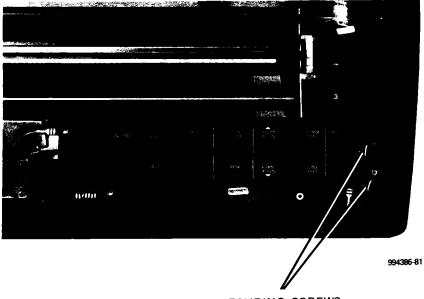

| 8.7.7   | Ribbon Drive Assembly                | 8-16        |

| 8.7.8   | Main/Auxiliary Control               |             |

|         | Panel                                | 8-18        |

| 8.7.9   | Carriage Drive Motor                 |             |

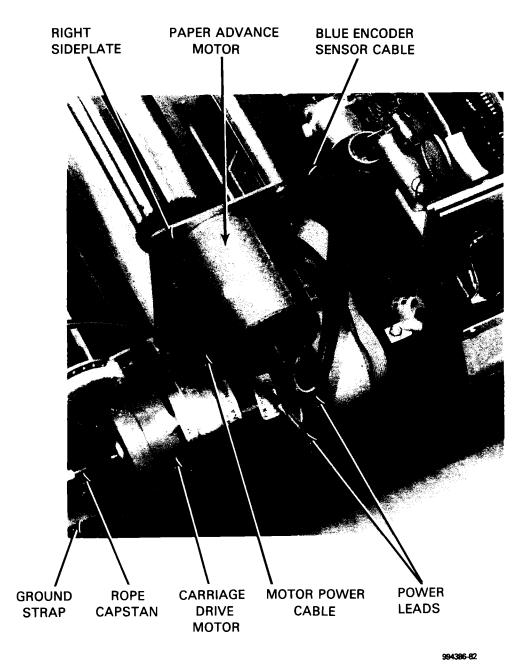

|         | Assembly                             | 8-19        |

| 8.7.10  |                                      | 8-22        |

| 8.7.11  | Carriage and Paper Drive             |             |

|         | Assembly                             |             |

| 8.7.12  |                                      | 8-25        |

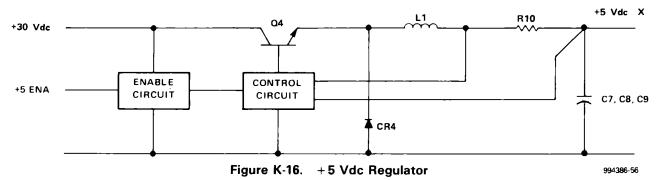

| 8.8     | + 5 Vdc Regulator                    |             |

|         | Adjustments                          |             |

| 8.9     | Testing                              | 8-26        |

| 9       | Assembly Drawings and<br>Parts Lists |             |

| 10      | Schematic Diagrams                   |             |

|         | APPENDIXES                           |             |

| Α       | Dot Matrix Character Generation      |             |

| В       | ASCII Control and Character Code     |             |

| С       | Model 810 Printer Versions,          |             |

|         | Options, and Accessories             |             |

| D       | TMS 8080A Microprocessor             |             |

| E       | TMS 5501 I/O Controller              |             |

| F       | Installation of Optional Kits        |             |

| G       | TMS 6011 Data Sheets                 |             |

| н       | Cable Pin Assignments                | _           |

| 1       | US ASCII/Katakana Dual Character     | Set         |

| J       | Strappable Options for Processor     |             |

|         | and Line Buffer Boards               |             |

| К       | Theory of Operation for Drive Board  | d           |

|         | (TI Part No. 994322) and Power       |             |

|         | Supply (TI Part No. 994394)          |             |

| L       | First-Generation Front Panels        |             |

|         | and Carriage Motor Assembly          |             |

vii

### LIST OF ILLUSTRATIONS

| Figure      | Title                                         | Page       |

|-------------|-----------------------------------------------|------------|

| 1-1         | Model 810 Printer                             | . 1-1      |

| 2-1         | Printer Dimensions                            | . 2-1      |

| 2-2         | Terminal Paper Basket<br>Installation         | 2-2        |

| 2-3         | Stand Paper Basket                            |            |

| 2-4         | Installation                                  |            |

| 2-4<br>2-5  | Ribbon Installation                           |            |

| 2-5<br>2-6  | Paper Loading                                 |            |

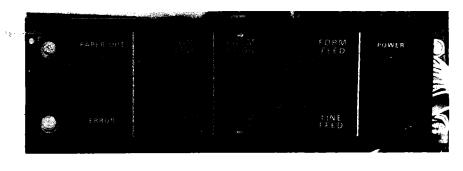

| 3-1         | Model 810 Printer Operator<br>Controls        | 2.1        |

| 3-2         | Model 810 Printer Control                     |            |

|             |                                               |            |

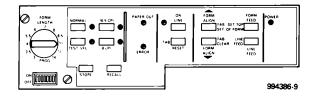

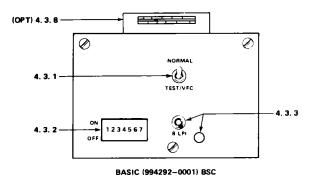

| 3-3         | Control Panel Options                         | . 3-3      |

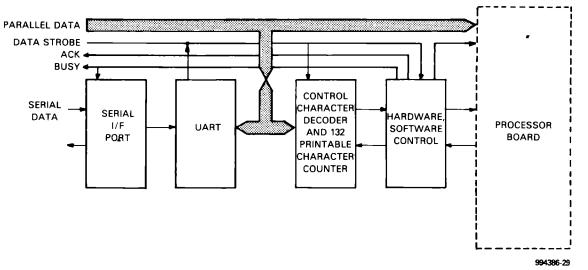

| 5-1         | Busy Signal Generation Block                  |            |

|             | Diagram (Printers without                     | <b>F</b> 4 |

| 5-2         | Line Buffer Option)                           | . 5-1      |

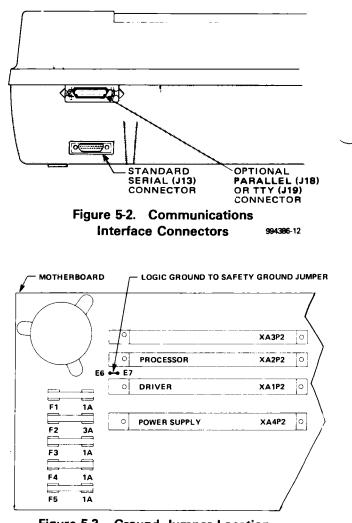

| <b>9-</b> Z | Connectors                                    | . 5-2      |

| 5-3         | Ground Jumper Location                        | . 5-2      |

| 00          | on the Motherboard                            | . 5-2      |

| 5-4         | Asynchronous Data Format                      |            |

| 5-5         | EIA or TTY Interface                          |            |

|             | BUSY Timing                                   | . 5-4      |

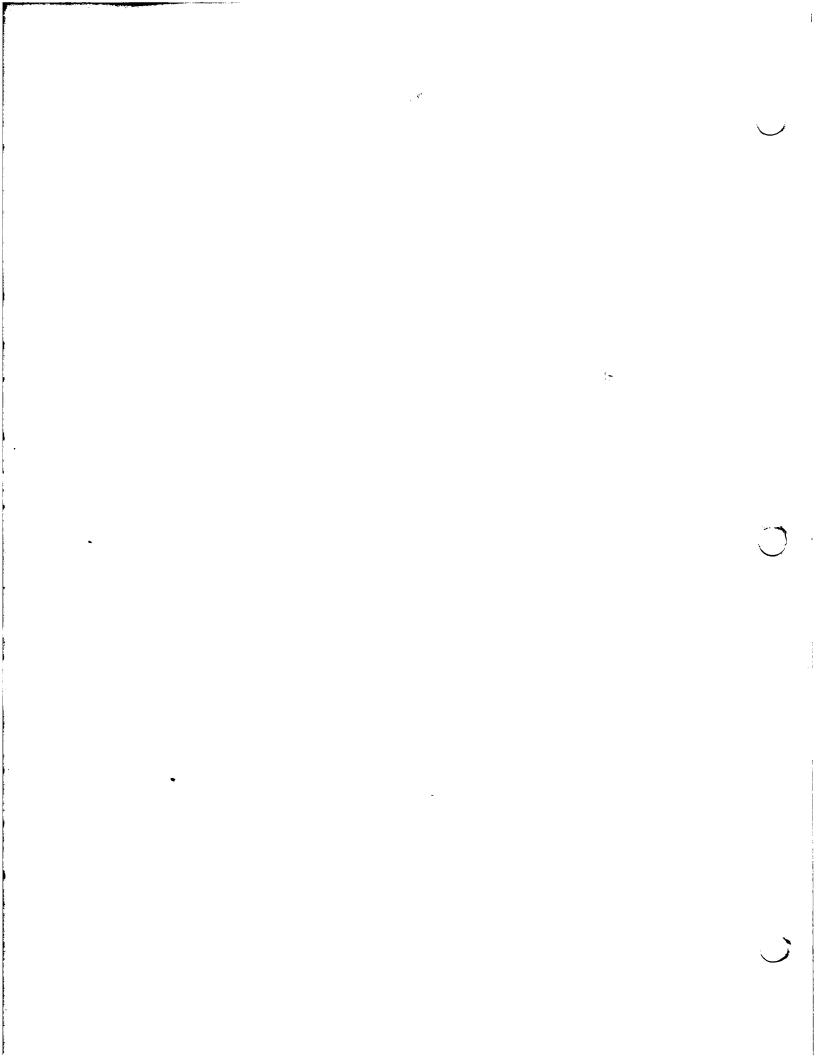

| 5-6         | Parallel (PLT) Interface<br>BUSY Timing       | . 5-5      |

| 6-1         | Busy Signal Generation Block                  |            |

| <b>V</b> -1 | Diagram (Printers with Line                   |            |

|             | Buffer Option)                                |            |

| 6-2         | Asynchronous Data Format                      | . 6-3      |

| 6-3         | EIA (LBE Option) and TTY                      |            |

|             |                                               | . 6-3      |

| 6-4         | Basic Parallel (LBP) Interface                |            |

|             | BUSY Timing, Line Buffer                      | <u>с</u> г |

|             | Option                                        | · 0-5      |

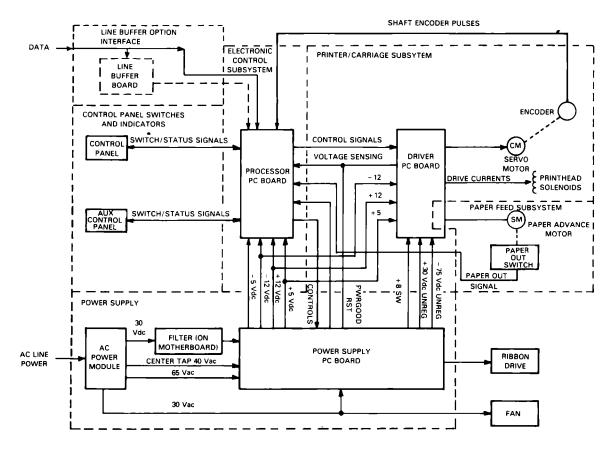

| 7-1         | Model 810 Printer Simplified                  | . 7-1      |

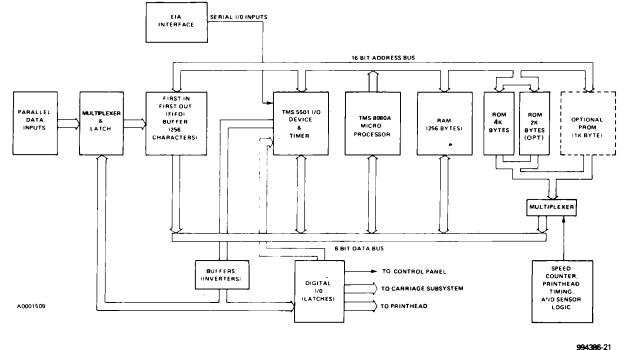

| 7-2         | Block Diagram<br>Electronic Control Subsystem | . /~1      |

| /-2         | Block Diagram                                 | 7-2        |

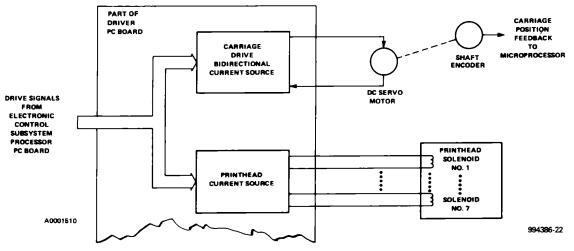

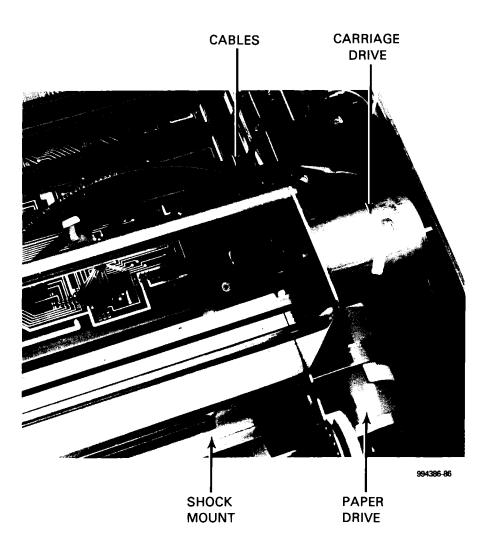

| 7-3         | Printhead Carriage Subsystem                  |            |

|             | Block Diagram                                 | 7-4        |

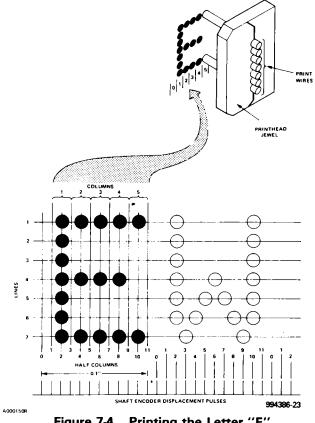

| 7-4         | Printing the Letter "E"                       |            |

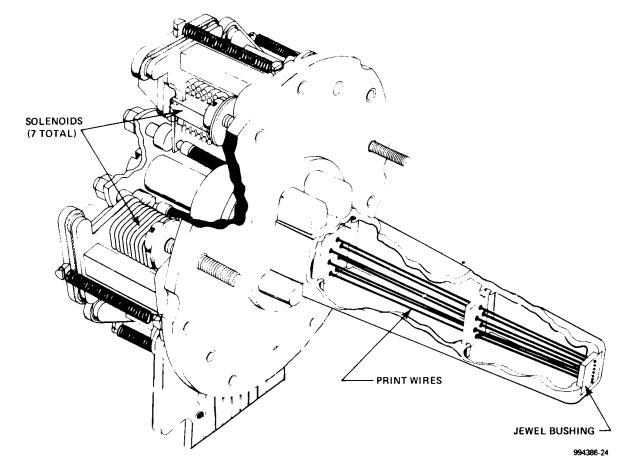

| 7-5         | Typical Model 810 Printer Printhea            |            |

|             | Assembly                                      |            |

| Figure | Title                                                                            | Page   | · - · |

|--------|----------------------------------------------------------------------------------|--------|-------|

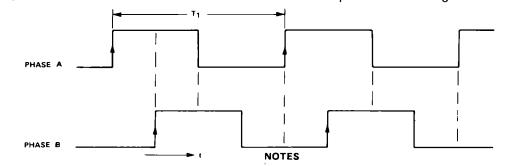

| 7-6    | Carriage Motor Shaft Encoder<br>Phase Relationship for<br>Left-to-Right Carriage |        |       |

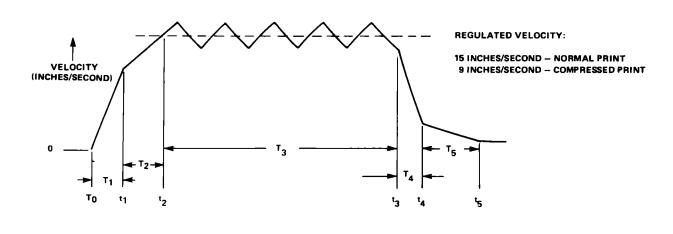

| 7-7    | Motion<br>Carriage Velocity Profile in                                           |        |       |

| 7-8    | Print Mode<br>Paper Feed Subsystem Block                                         |        |       |

| 7-9    | Diagram<br>Model 810 Printer Power Supply                                        |        |       |

| 7-10   | Block Diagram<br>Simplified Line Buffer Interface                                |        |       |

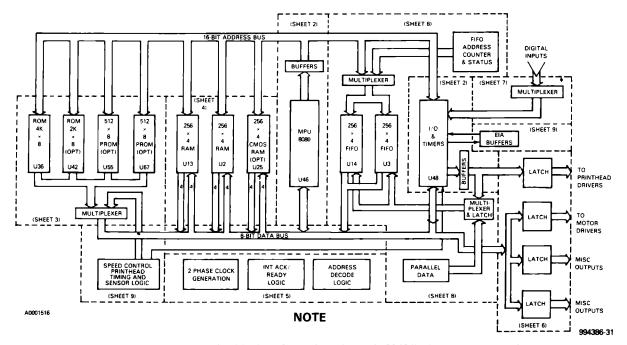

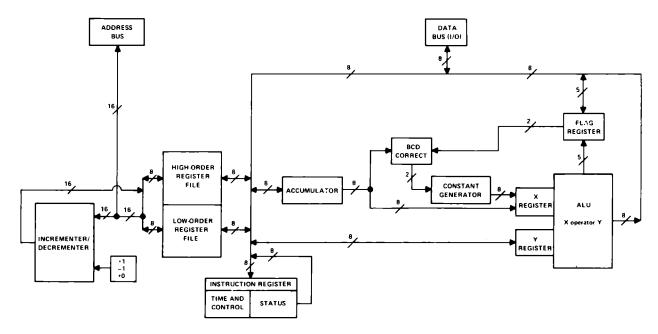

| 7-11   | Block Diagram<br>Model 810 Printer Simplified<br>Electronics Block Diagram       |        |       |

| 7-12   | Processor PC Board, Detailed<br>Block Diagram                                    |        |       |

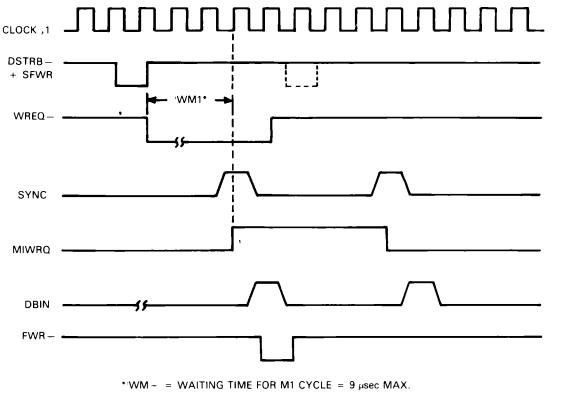

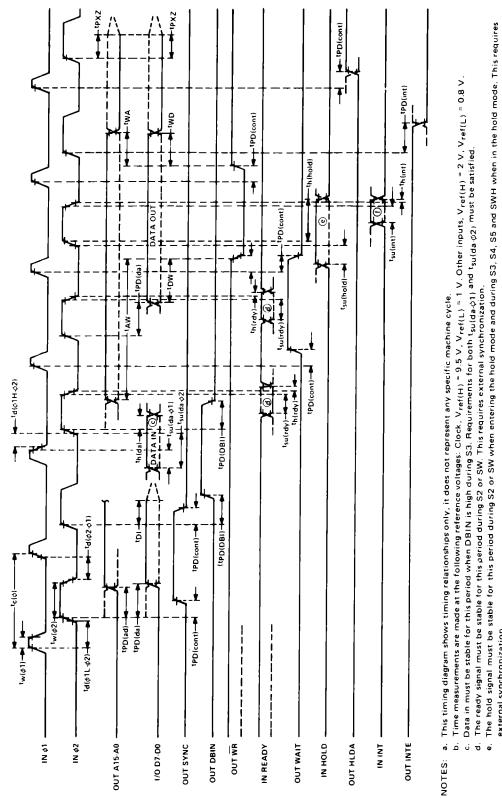

| 7-13   | FIFO Memory Write Cycle<br>Timing Diagram                                        |        |       |

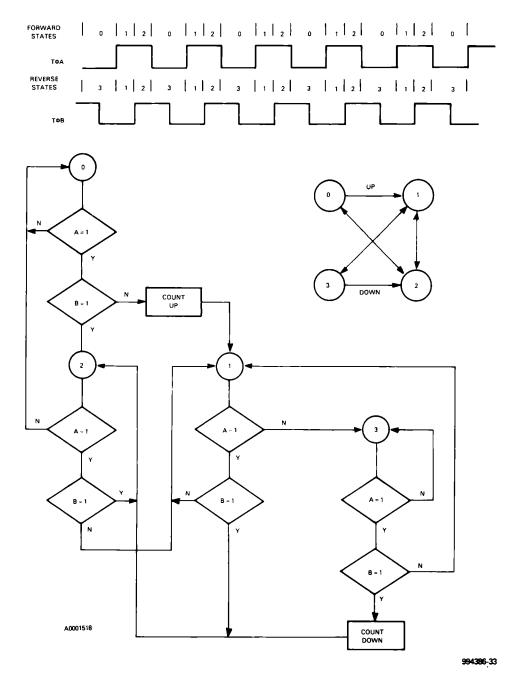

| 7-14   | Carriage Motor Shaft Encoder<br>State Diagram                                    |        |       |

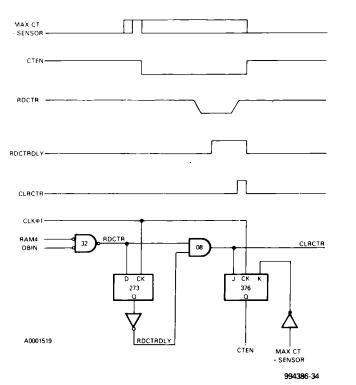

| 7-15   | Carriage Speed Control Counter<br>Timing Diagram                                 |        |       |

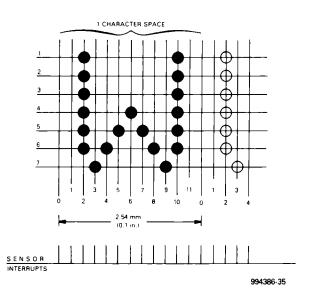

| 7-16   | Forming the Character "W"                                                        | . 7-16 |       |

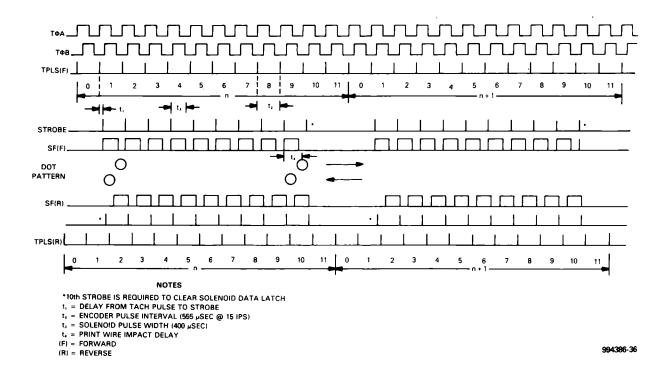

| 7-17   | Printhead Solenoid Timing<br>Diagram                                             |        | )     |

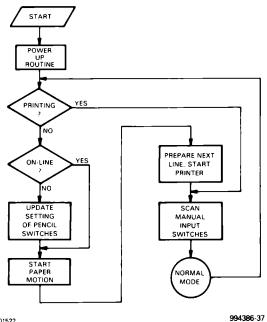

| 7-18   | Normal Print Mode<br>Flowchart                                                   |        |       |

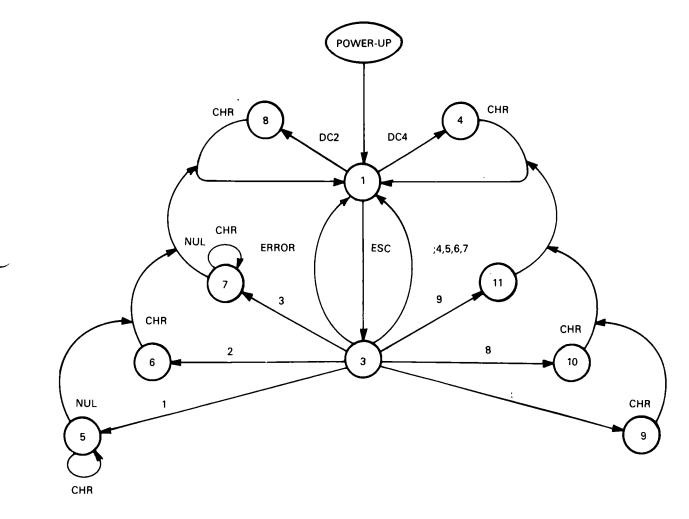

| 7-19   | Printer Subroutine E100<br>Accept State Diagram                                  |        |       |

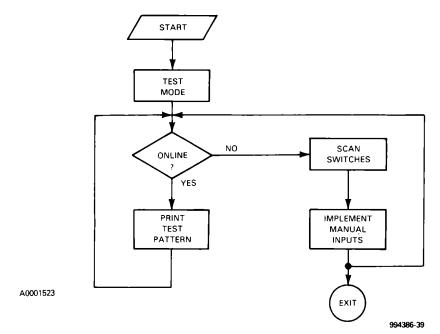

| 7-20   | Test Mode Flowchart                                                              |        |       |

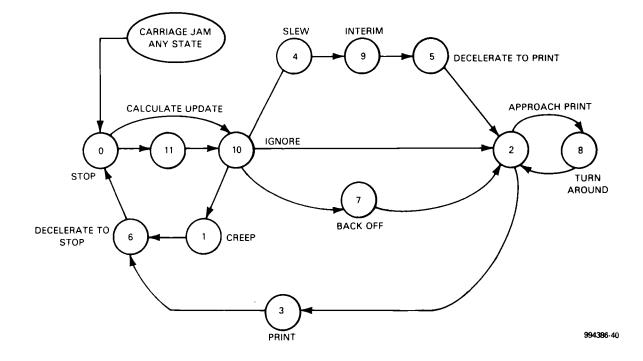

| 7-21   | Printhead Carriage State<br>Diagram                                              | . 7-21 |       |

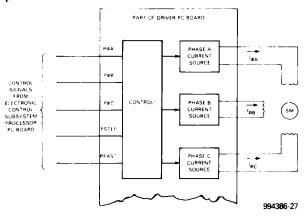

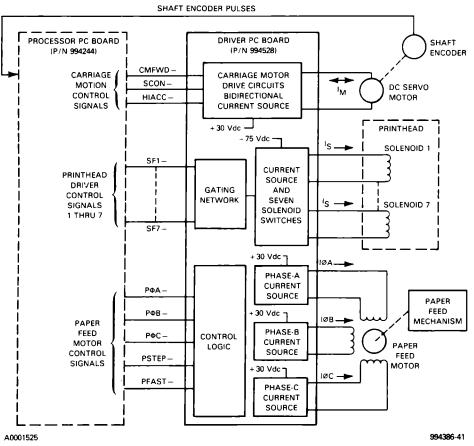

| 7-22   | Driver PC Board Block<br>Diagram                                                 |        |       |

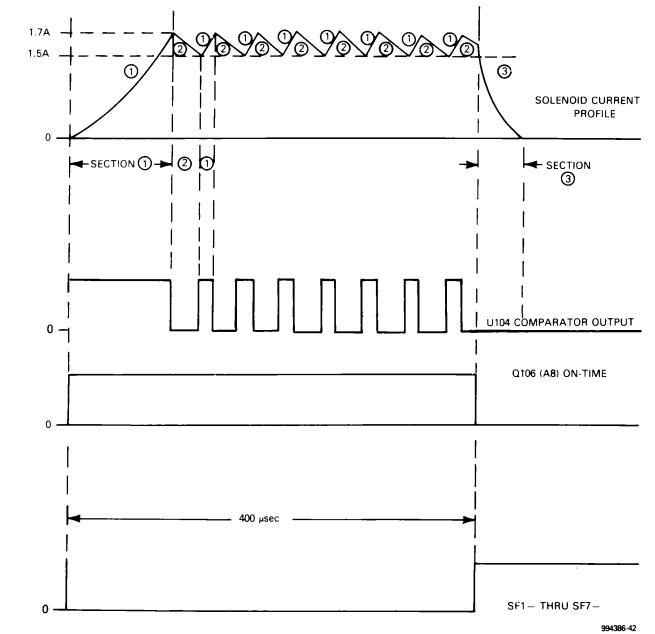

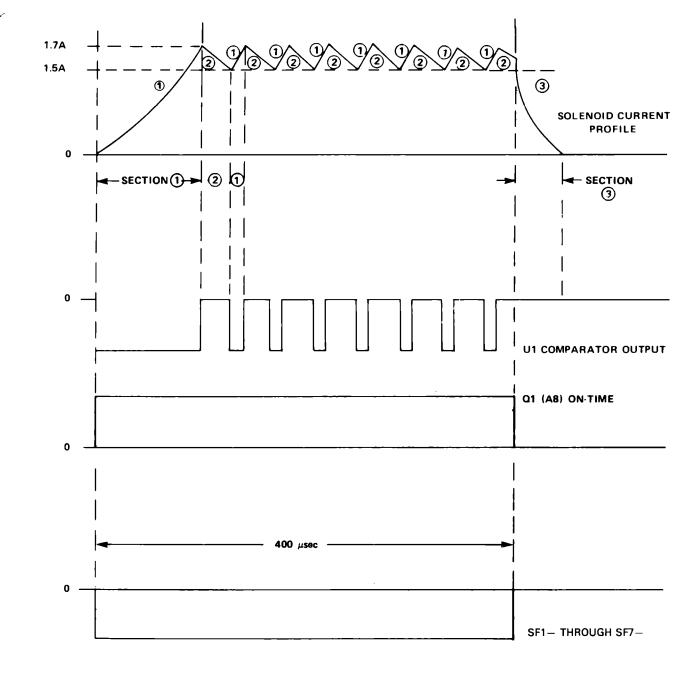

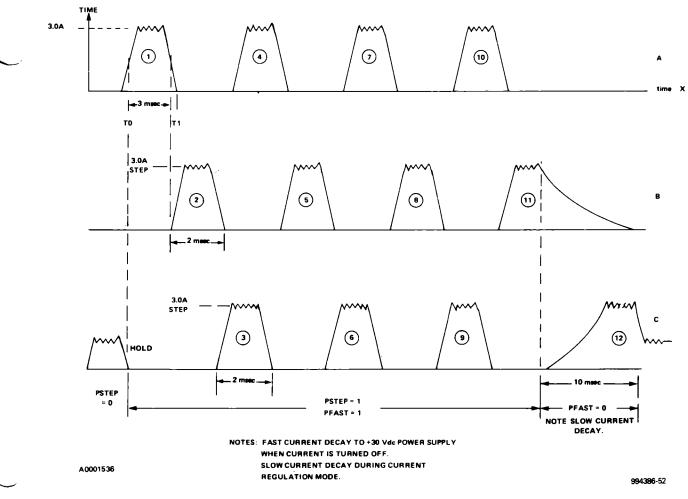

| 7-23   | Printhead Solenoid Current<br>Pulse Profile                                      |        |       |

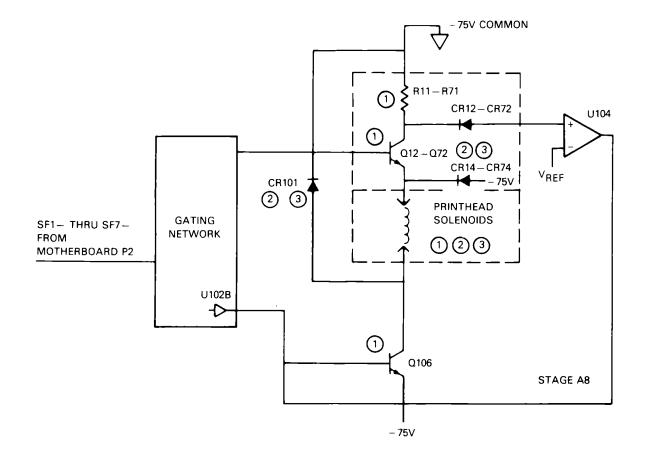

| 7-24   | Printhead Power Driver<br>Simplified Schematic                                   |        |       |

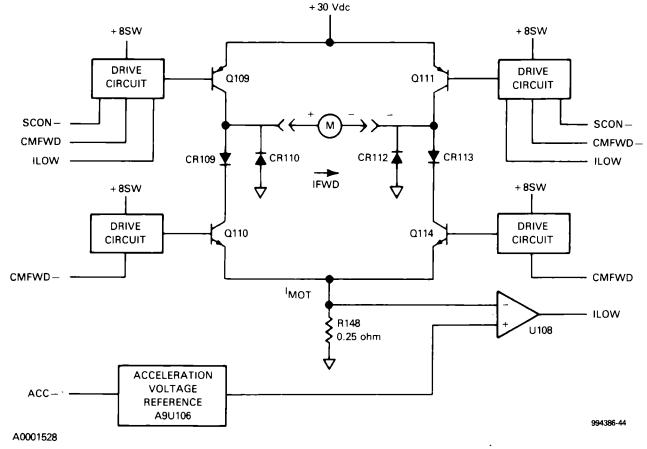

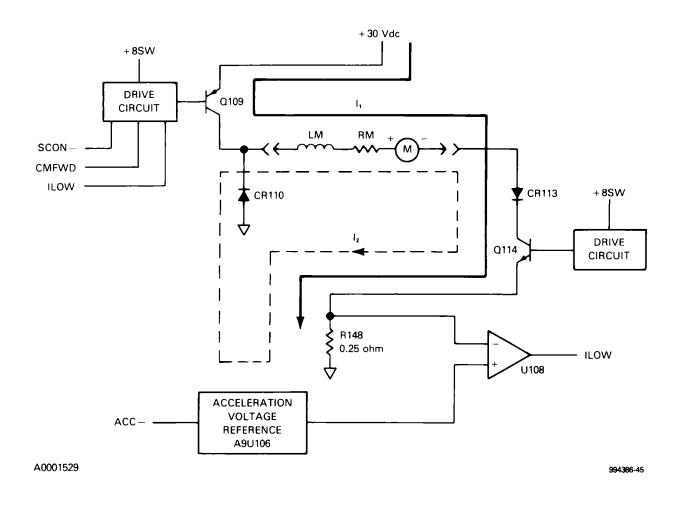

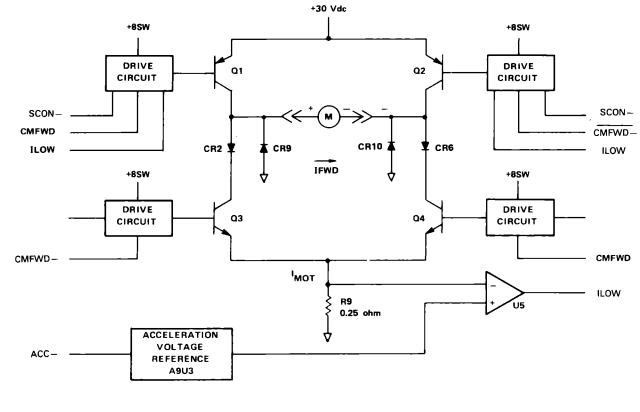

| 7-25   | Printhead Carriage Driver<br>Simplified Schematic                                | . 7-25 |       |

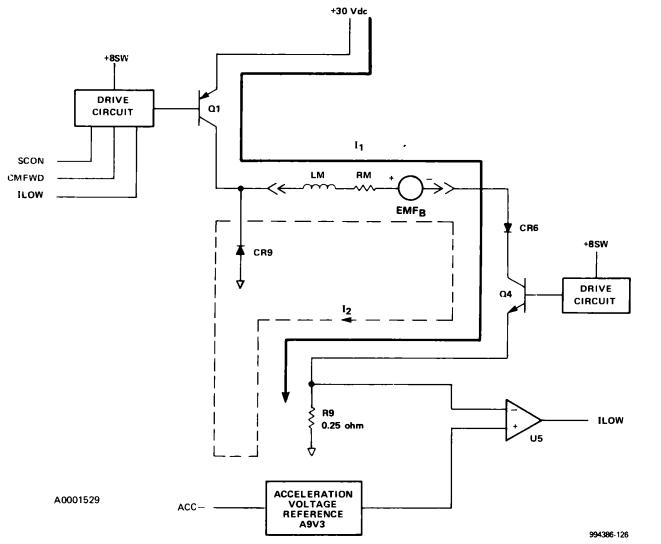

| 7-26   | Printhead Carriage Driver<br>Circuit Forward Command                             | . 7-26 |       |

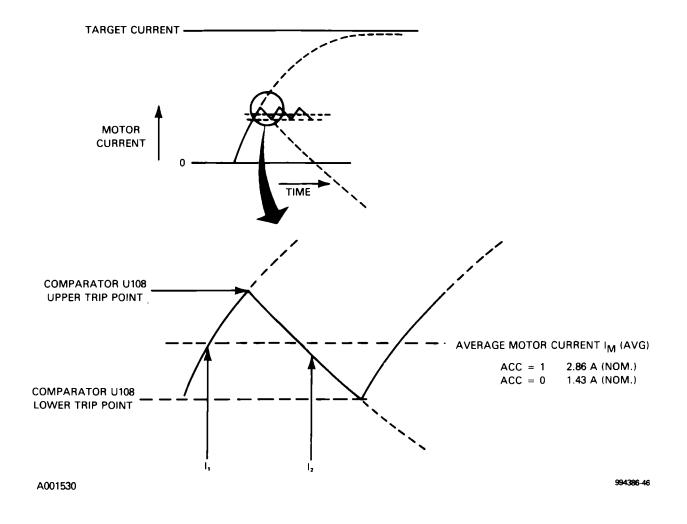

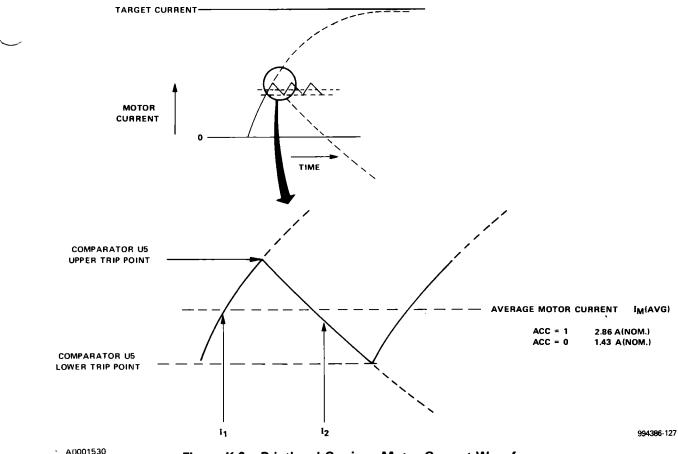

| 7-27   | Printhead Carriage Motor<br>Current Waveforms                                    | . 7-27 |       |

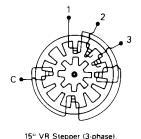

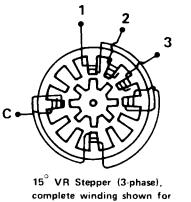

| 7-28   | Variable Reluctance, Paper<br>Feed Stepper Motor                                 |        |       |

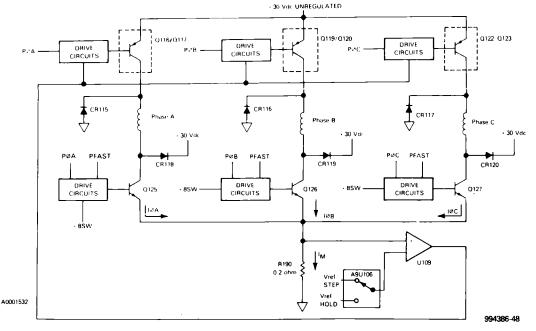

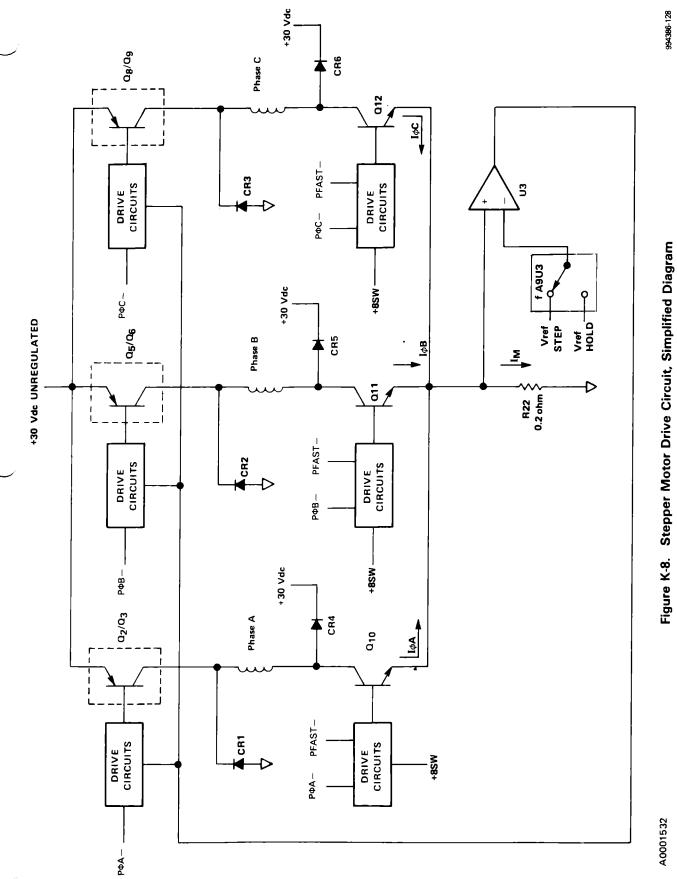

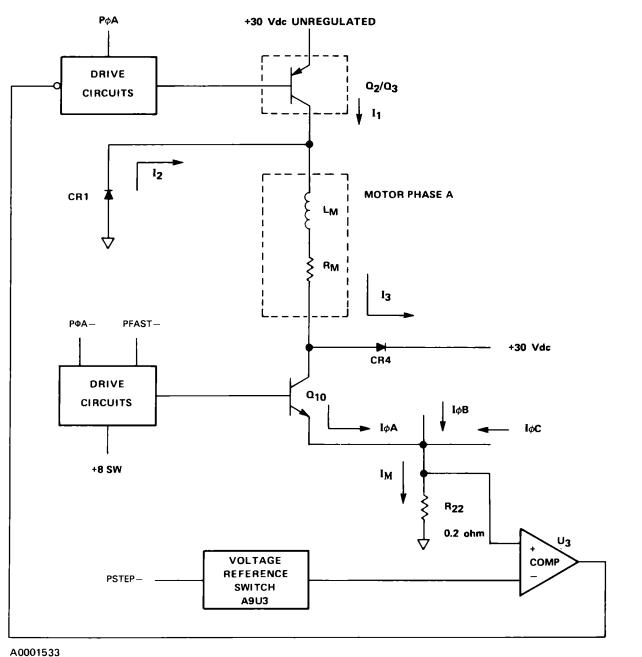

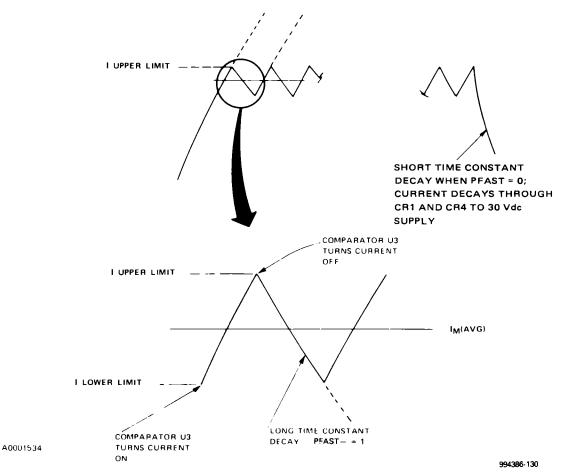

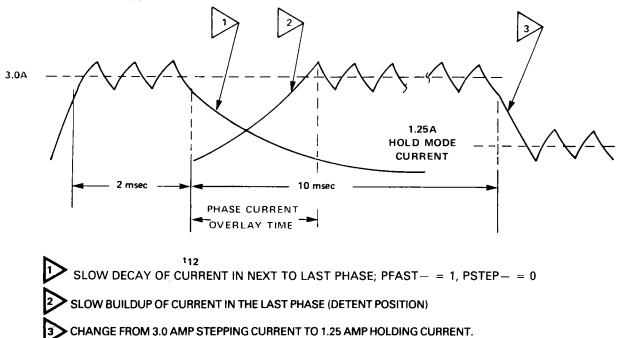

| 7-29   | Stepper Motor Drive Circuit,<br>Simplified Diagram                               |        |       |

×.

| Title                                                                                           | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

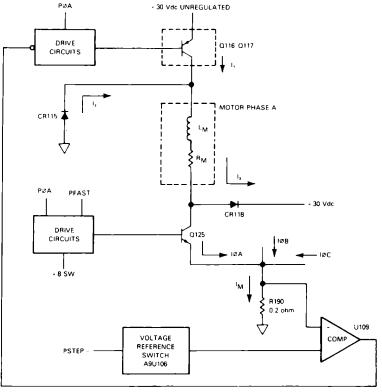

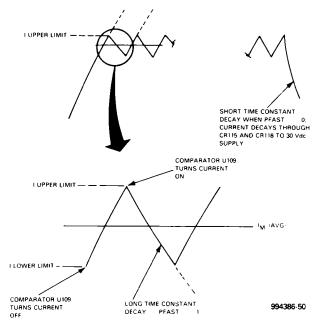

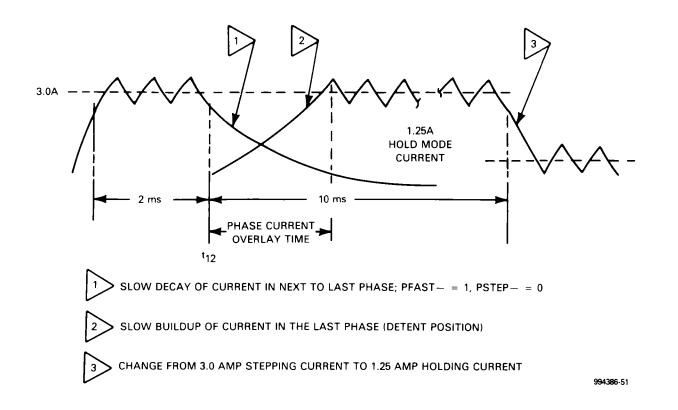

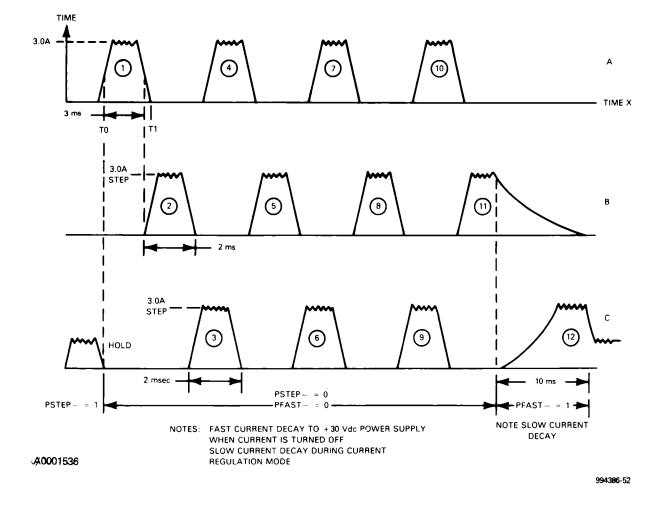

| Stepper Motor Drive Circuit,                                                                    | 7-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Stepper Motor Circuit                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Waveforms         Mathematical Stepper           Paper Feed Stepper Motor         Stepper Motor | . 7-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                 | 7-32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Feed Cycle                                                                                      | 7-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

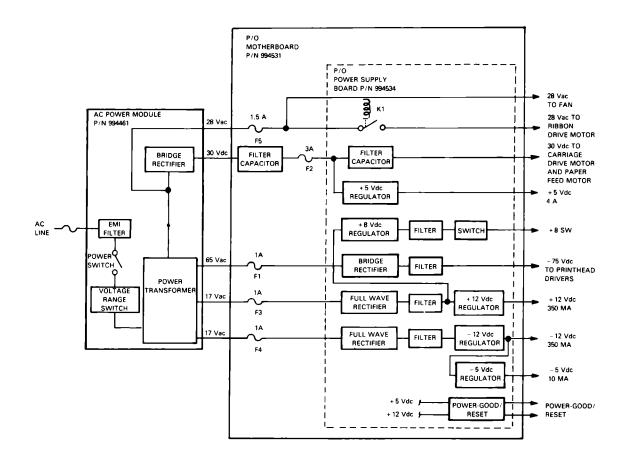

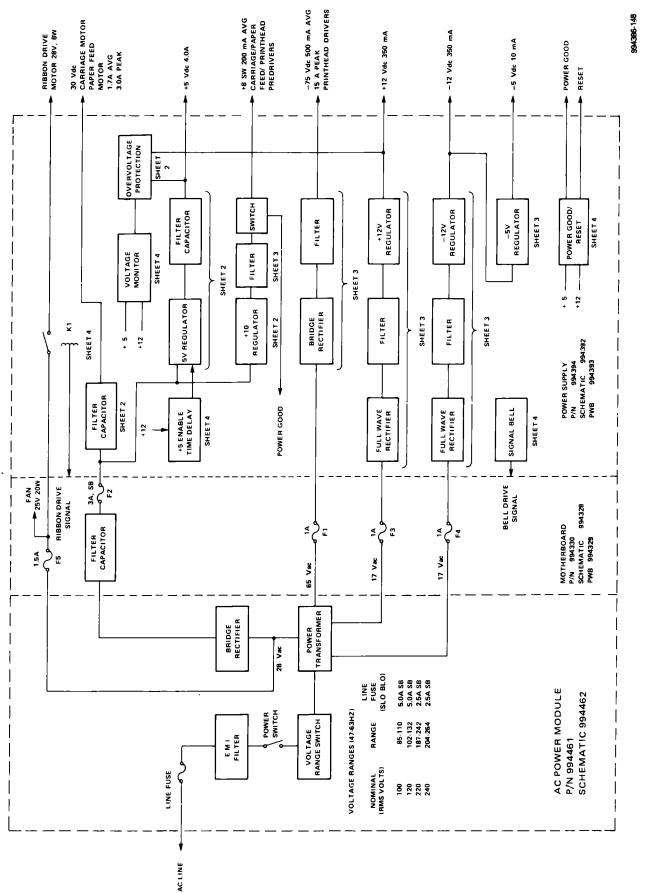

|                                                                                                 | 7-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

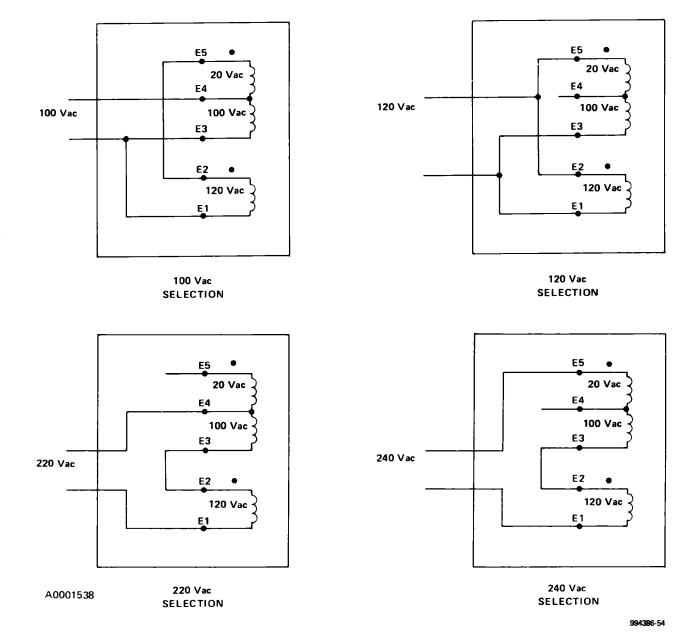

| Power Transformer Primary                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

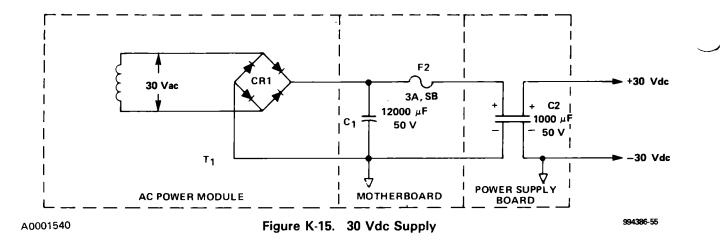

|                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| _                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| -                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

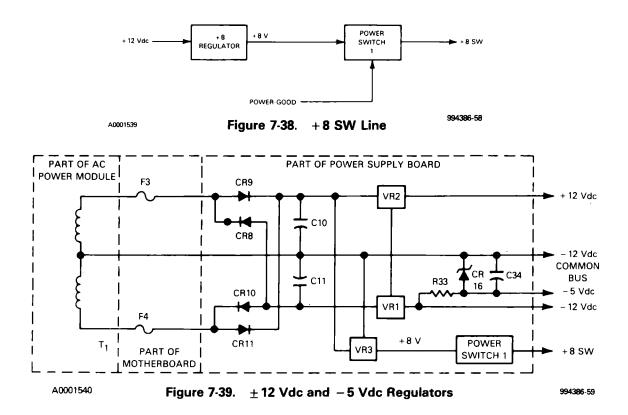

|                                                                                                 | 7-37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                 | 7-37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

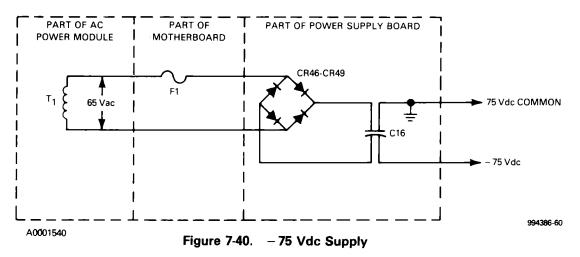

|                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

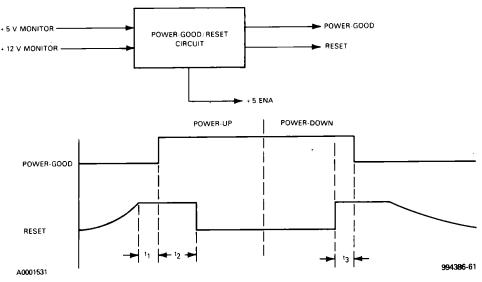

|                                                                                                 | 7-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

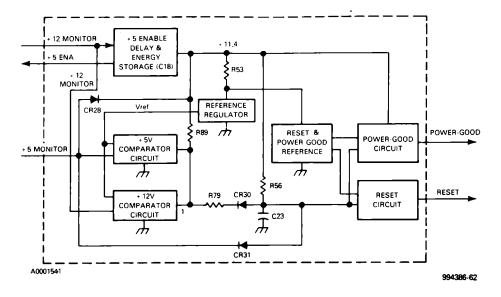

| Power-Good/Reset Circuit                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                 | 7-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| •                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                 | 7-43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| •                                                                                               | 7-43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                 | 8-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Paper Advance Lubrication                                                                       | 0 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                 | Stepper Motor Drive Circuit,<br>Phase A<br>Stepper Motor Circuit<br>Waveforms<br>Paper Feed Stepper Motor<br>Currents<br>Stepper Motor Line<br>Feed Cycle<br>Power Supply Functional<br>Block Diagram<br>Power Transformer Primary<br>Tap Arrangements<br>30 Vdc Supply<br>+ 5 Vdc Regulator<br>+ 5 Vdc Regulator<br>+ 5 Vdc Regulator<br>+ 8 SW Line<br>± 12 Vdc and - 5 Vdc<br>Regulators<br>- 75 Vdc Supply<br>Power-Good/Reset Signal<br>Profiles<br>Power-Good/Reset Circuit<br>Block Diagram<br>Line Buffer Option Modification<br>of 810 Firmware<br>Block Diagram<br>Line Buffer Option Software<br>Block Diagram |

| Figure      | Title                        | Page          |

|-------------|------------------------------|---------------|

| 8-4         | Power Fuse at Rear of        |               |

|             | Printer                      |               |

| 8-5         | Printhead Removal            | . 8-5         |

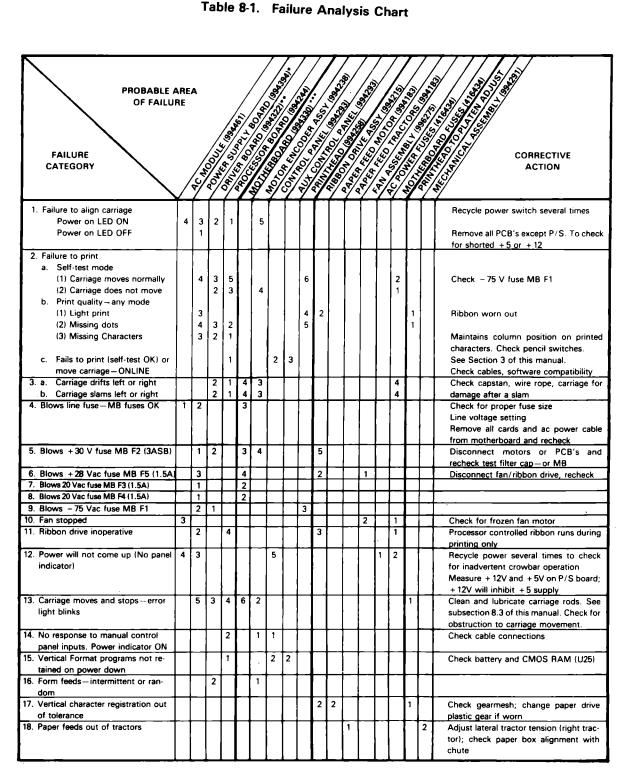

| 8-6         | Printed Circuit Board        |               |

|             | Removal                      |               |

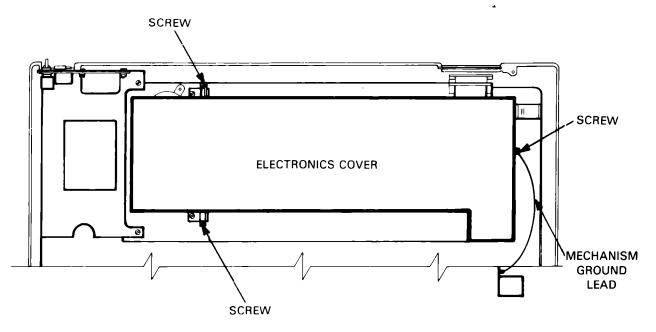

| 8-7         | Electronics Cover Removal    |               |

| 8-8         | AC Power Module              |               |

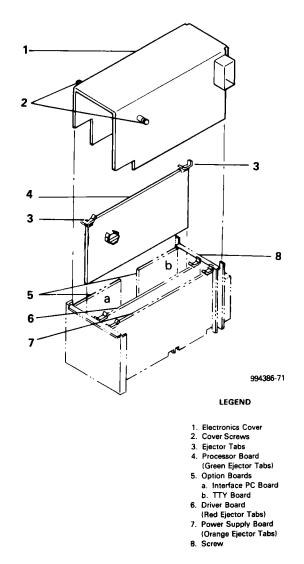

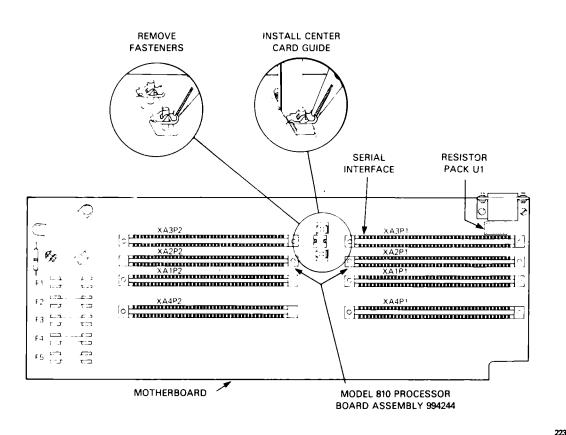

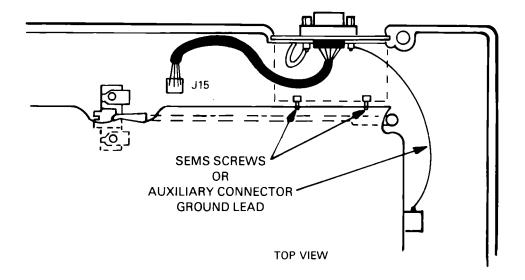

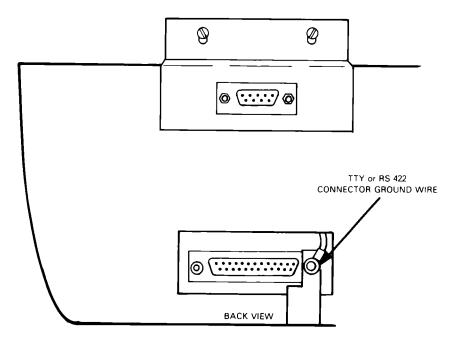

| 8-9         | Motherboard                  | . 8-10        |

| 8-10        | Fan, Card Guide,             |               |

|             | and Bracket                  | . 8-11        |

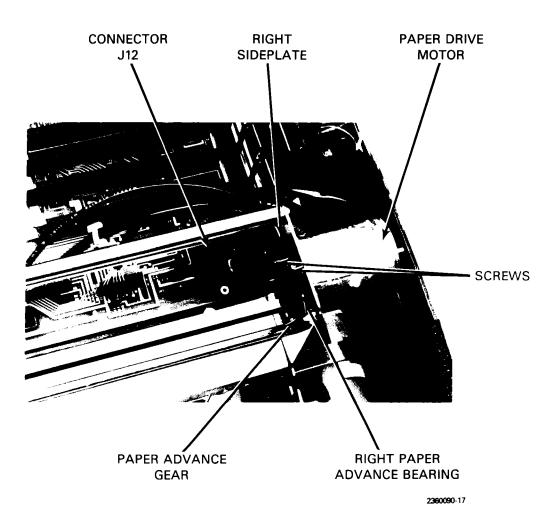

| 8-11        | Paper Drive Motor with Gear, |               |

|             | Connector, and Shaft         |               |

|             | Removed                      | . 8-12        |

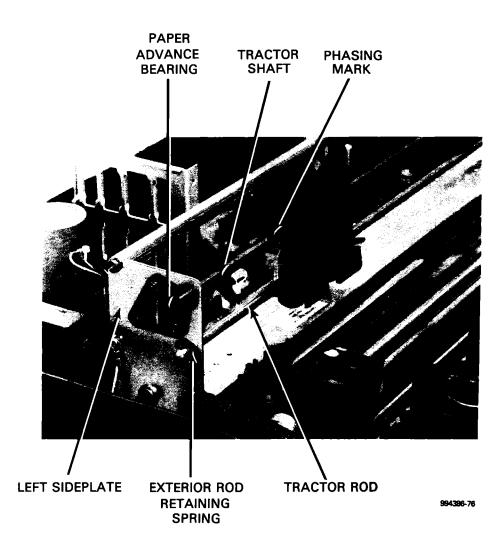

| 8-12        | Left Paper Advance           |               |

|             | Bearing                      | . 8-13        |

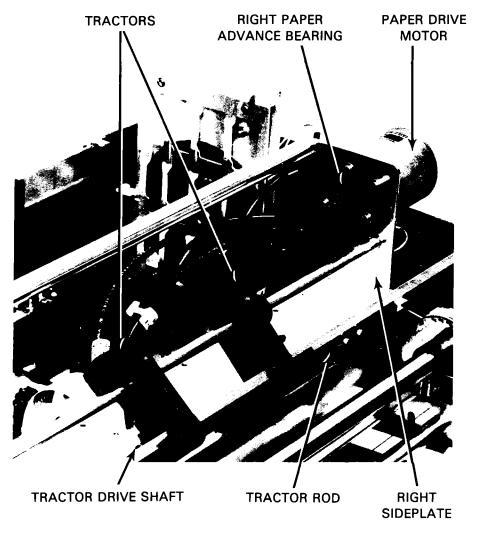

| 8-13        | Paper Tractors Removal,      |               |

|             | Right Side View              | . 8-14        |

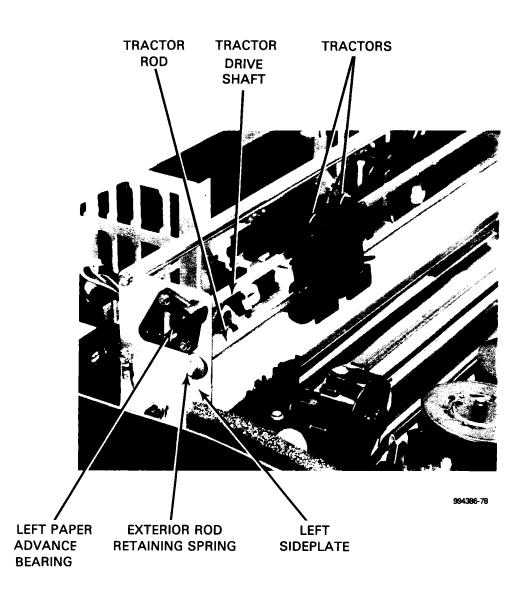

| 8-14        | Paper Tractors Removal,      |               |

|             | Left Side View               |               |

| 8-15        | Ribbon Drive Assembly        | . 8-16        |

| 8-16        | Ribbon Drive Assembly        |               |

|             | Removal                      | . 8-17        |

| 8-17        | Main/Auxiliary Control       |               |

|             | Panel                        |               |

| 8-18        | Carriage Drive Motor         |               |

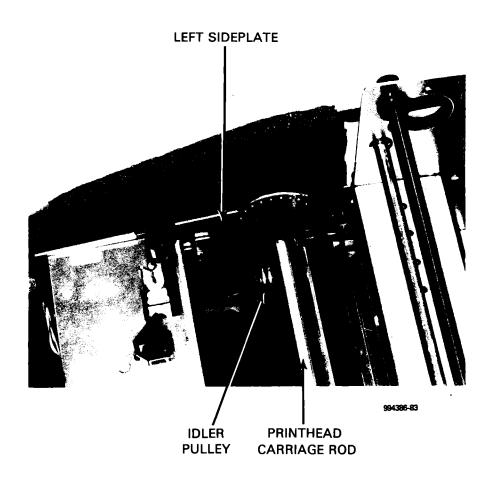

| 8-19        | Idler Pulley                 |               |

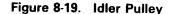

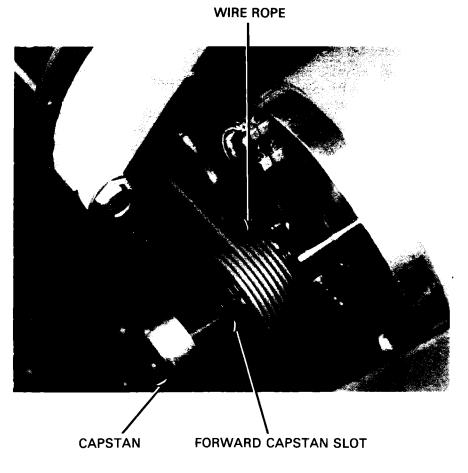

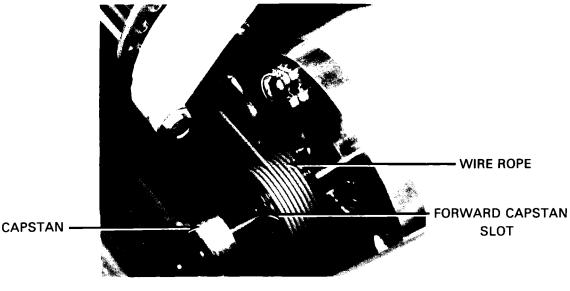

| 8-20        | Wire Rope Detail             |               |

| 8-20a       | Wire Rope Detail             | . <b>8-22</b> |

| 8-21        | Carriage and Paper Drive     |               |

|             | Assembly                     |               |

| 8-22        | Paper-Out Switch             |               |

| 8-23        | Secondary Fuse Area          |               |

| 8-24        | Test Barberpole Printout     | . 8-27        |

| <b>9</b> -1 | Model 810 Printer            |               |

|             | Major Assemblies             | . <b>9-3</b>  |

1

### LIST OF TABLES

| Table | Title                                             | Page       |

|-------|---------------------------------------------------|------------|

| 1-1   | Standard Model 810 Printer<br>Characteristics and |            |

|       | Specifications                                    | . 1-2      |

| 3-1   | Control Panel Configurations                      | . 3-2      |

| 3-2   | Control Panel Baud Rate                           |            |

| ~ ~   | Selections                                        | . 3-6      |

| 3-3   | Control Panel Parity                              | 27         |

|       | Selections                                        | . 3-7      |

| 4-1   | Software Commands (for Printers                   | 6          |

|       | without Line Buffer Option)                       | . 4-2      |

| 4-2   | Software Control Column or                        |            |

|       | Line "n" Number Equivalents                       | 4-4        |

| 4-3   | Software Commands (for                            |            |

|       | Printers with Line Buffer                         |            |

|       | Option)                                           | . 4-5      |

| 5-1   | Serial Interface Connector                        |            |

|       | Signals (J13)                                     | . 5-3      |

| 5-2   | Parallel Interface Connector                      |            |

|       | Signals (J18), PLT Printers                       | . 5-4      |

| 5-3   | TTY Current Loop Interface                        | <b>F</b> 0 |

|       | Signals (J19)                                     | · 5-6      |

,

| Table | Title                                                     | Page   |

|-------|-----------------------------------------------------------|--------|

| 5-4   | RS-422 Interface Signals                                  | 5-7    |

| 5-5   | RS-422 Logic Convention                                   | · 5-7  |

| 6-1   | Serial Interface Connector<br>Signals (J13), LBE Printers | . 6-2  |

| 6-2   | Parallel Interface Connector<br>Signals (J18), LBP        |        |

|       | Printers                                                  | . 6-4  |

| 6-3   | TTY Current Loop Interface                                |        |

|       | Signals with Line Buffer                                  |        |

|       | Option                                                    | . 6-6  |

| 7-1   | Printhead Subroutine E100                                 |        |

|       | Accept States                                             | . 7-18 |

| 7-2   | Carriage State Maximum                                    |        |

|       | Software Execution Times                                  | 7 20   |

| 7-3   | (Microseconds)                                            | . /-20 |

| 7-3   | Carriage Motion Reference<br>Speeds                       | 7-21   |

| 7-4   | Baud Rate Selection Table                                 |        |

|       |                                                           | . / 46 |

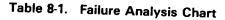

| 8-1   | Failure Analysis Chart                                    | . 8-6  |

| 8-2   | Option PROM TI Part Number                                |        |

|       | and Location                                              | . 8-28 |

# **Section 1**

# **General Description**

### **1.1 STANDARD FEATURES**

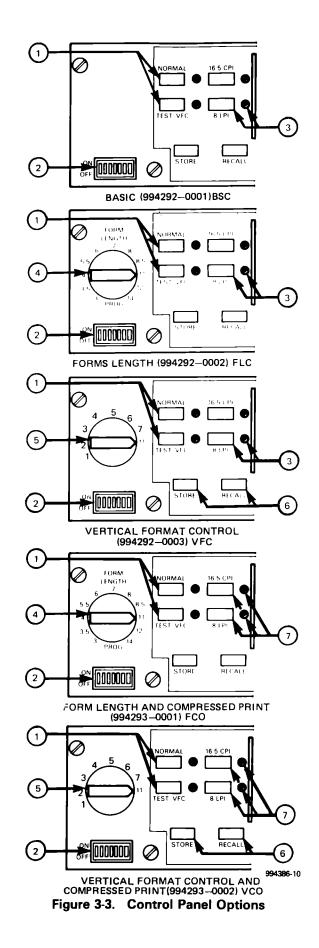

The Texas Instruments *Omni 800* Model 810 printer is a receive-only, forms-programmable, impact printer. It features a microprocessor system which controls all character recognition, printing, and paper movement. Basic operating, data processing, and self-test routines for the microprocessor system are stored in read-only memory (ROM). Random-access memory (RAM) stores vertical format control routines which may be locally programmed by the operator or remotely programmed through the communications line.

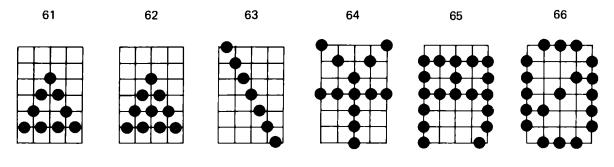

A single seven-dot-column printhead produces the nine-by-seven dot matrix for character generation (see Appendix A). The 64-character, limited-ASCII, 95-character set (see Appendix A) and other character sets are available as options. Printing is bidirectional at the rate of 150 characters per second. A full 132-character line is printed in less than one second.

The standard print format is ten characters per inch (cpi) horizontally and six or eight lines per inch (lpi) vertically. Options are available to produce compressed printing (16.5 cpi) and/or expanded printing (five cpi). The printer produces one original and up to five copies using sprocketfed paper in widths from 76.2 to 381 mm (3 to 15 in.).

In addition to the standard, serial EIA interface, a parallel (option code PLT) interface or a TTY/RS-422 interface is also available as an option. The Line Buffer option is available in three interface configurations: EIA (option code LBE), parallel (option code LBP), or TTY current loop (option code LBT).

Figure 1-1. Model 810 Printer

### **1.2 CONFIGURATIONS**

The Model 810 is available in five versions:

| TI Part Number | Code | Version                                           |

|----------------|------|---------------------------------------------------|

| 994292-0001    | BSC  | Basic                                             |

| 994292-0002    | FLC  | Forms Length<br>Control                           |

| 994292-0003    | VFC  | Vertical Format<br>Control                        |

| 994293-0001    | FCO  | Forms Length<br>Control, Com-<br>pressed Print    |

| 994293-0002    | VCO  | Vertical Format<br>Control, Com-<br>pressed Print |

| 2360013-0001   | PKG  | Package                                           |

Any options installed in your printer are listed on a label affixed to the underside of the access door. The options are identified by a three-letter configuration code.

### **1.3 SPECIFICATIONS**

Standard features and specifications are listed in Table 1-1.

### Table 1-1. Standard Model 810 Printer Characteristics and Specifications

| Characteristic                       | Specification                                              | Characteristic                       | Specification                               |

|--------------------------------------|------------------------------------------------------------|--------------------------------------|---------------------------------------------|

| PRINTING                             |                                                            | COMMUNICATIONS                       |                                             |

| Technique                            | Seven-wire matrix, impact                                  | Interface                            | Serial (EIA RS-232-C)                       |

| Character matrix                     | 9 $\times$ 7 (9 wide, 7 high)<br>dot matrix                | Baud rates                           | 110, 150, 300, 1200, 2400,<br>4800, 9600    |

| Character set<br>Characters per inch | 64-character limited ASCII<br>10                           | Parity                               | ODD, EVEN or ignore                         |

| Characters per line                  | 132 maximum                                                | INPUT POWER                          |                                             |

| Lines per inch                       | 6 or 8 (operator—or<br>software—selectable)                | ac voltage                           | 100, 120, 220, or 240 Vac<br>(+10% to -15%) |

|                                      |                                                            | Frequency                            | 48 to 62 Hz                                 |

| THROUGHPUT                           |                                                            | Watts                                | 200                                         |

| Print speed                          | 150 characters per second                                  | Power fuse                           | 100 or 120 Vac range, 5 A,                  |

| Lines per minute                     | 64 at 132 characters per line,                             |                                      | 250 V fuse                                  |

|                                      | and up to 450 at 10 cpl                                    |                                      | 220 or 240 Vac range, 2.5 A,<br>250 V fuse  |

| Line feed                            | 33 milliseconds                                            | 4                                    |                                             |

| Paper slew                           | 170 mm per second                                          | ENVIRONMENTAL                        |                                             |

|                                      | (6.67 in/sec)                                              | Mounting                             | Table top                                   |

| PAPER HANDLING                       |                                                            | Operating temperature                | +5°C (+37°F) to +40°C<br>(+104°F)*          |

| Paper width                          | Adjustable from 76 to 381<br>mm (3 to 15 in.)              | Storage temperature                  | - 30°C (-22°F) to +70°C<br>(+158°F)         |

| Paper loading                        | Rear or bottom feed                                        | Operating humidity                   | 10% to 90% (no condensation)                |

| Number of copies                     | One original and five copies                               | Storage humidity                     | 5% to 95% (no condensation)                 |

| CONTROL SYSTEM                       |                                                            | PHYSICAL                             |                                             |

| Electronics                          | 8080 microprocessor system                                 | Weight                               | 25 kg (55 pounds)                           |

| Printing method                      | Bidirectional                                              | Height                               | 203 mm (8 inches)                           |

| Buffer (FIFO)                        | 256 characters                                             | Width                                | 654 mm (25.75 inches)                       |

| Horizontal tabs                      | Software Programmable                                      | Depth                                | 508 mm (20 inches)                          |

| Vertical format control              | Software and operator<br>programmable                      |                                      |                                             |

| Self-test                            | Prints ASCII characters in a rotating pattern (barberpole) | *Up to 2134 m (7000 feet) M          | ASL. Derate linearly to 25°C                |

| Bell                                 | Pulsing audible tone                                       | (+77°F) at 3048 m (10,000 feet) MSL. |                                             |

-

### **1.4 MODIFIABLE FEATURES**

The following standard operating option is easily modified in the field on the standard Model 810 printer. See Appendix F for jumper configuration.

Signal and safety ground isolation by a capacitor (ISC option).

The following standard operating options are easily modified in the field on the standard Model 810 printer without the Line Buffer option. See Appendix F for jumper configurations.

- Enable or disable recognition of DEL character (NDE option)

- BUSY or NOT BUSY on DTR line (DNB option)

- Inverted reverse channel (IRC option) signal

- Enable or disable recognition of DC1-DC3 characters (DCO option).

The following standard operating options are easily modified in the field on the standard Model 810 printer with the Line Buffer option. See Appendix F for jumper configurations.

- BUSY or NOT BUSY on the DTR line (DNB option)

- Inverted reverse channel signal (IRC option)

- Enable or disable gated EIA data (GED option)

- Enable or disable half-duplex operation (HDP option)

- Enable or disable carriage return detect (DSC option)

- Enable or disable gated data strobe (GDS option)

- Enable or disable recognition of DC1-DC3 characters (DCO option).

### **1.5 OPTIONAL FEATURES**

The following character sets\* and optional features (identified by configuration code in parentheses) are available for the Model 810 printer:

- Full U.S. ASCII 95-character set (FUL)

- Full U.S. ASCII/Katakana dual-character set (KAT, KTS)

- European (DNF, DNL, SWF, SWL, UKF, or UKL) and other character sets

- Parallel interface (PLT)

- TTY, 20-mA, neutral current loop (TTY)

- Line Buffer option PC board, EIA interface (LBE)

- Line Buffer option PC board, parallel interface (LBP)

- Line Buffer option PC Board, with TTY, 20-mA, neutral current loop (LBT)

- Selectable form lengths (FCO or FLC)

- Vertical Format Control, nonvolatile eight-channel memory (VCO or VFC)

- Compressed Print, 16.5 cpi (FCO or VCO)

- Expanded Print option (EXP) prints five cpi and 8.25 cpi.The EXP option is available only with the standard 64-character ASCII character set. The 8.25 cpi option is available on FCO and VCO printers only.

- Nine-copy printhead nine copies can be printed.

### **1.6 ACCESSORIES**

The following accessories are available for use

<sup>\*</sup>Only one character set option may be specified in the Model 810 printer.

with the Model 810 printer:

- Tear bar

- Paper baskets for terminal or floor stand

¥.-

- Floor-mounting stand

- Interface cables (see cabling information in Section 5 or 6 and Appendix H).

# Section 2

# Installation

### 2.1 INTRODUCTION

This section provides information for selecting the installation site, unpacking and setting up the printer, and ensuring that the printer is operating properly. Communications line connections to the Model 810 printer are described in Sections 5 and 6 of this manual.

### 2.2 SPACE REQUIREMENTS

The printer should be located to allow easy access to the operator controls and printed output. If the optional floor stand is not used, a sturdy table capable of supporting 25 kg (55 lbs.) is considered suitable.

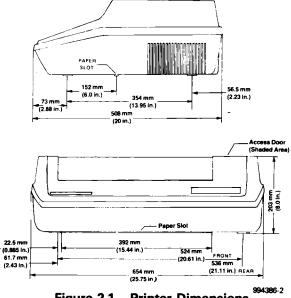

The printer occupies a flat surface area 654 mm (25.75 in.) wide by 584 mm (23 in.) deep, including a cable clearance of 76 mm (3 in.). See Figure 2-1 for visual dimensions.

Regardless of the supporting device, care must be taken to ensure that neither the weight of the printer nor other types of pressure are exerted on the paper chute which could deform it. Additionally, an unobstructed paper feed path below or behind the printer must be provided. If the paper basket accessory is not selected, some method of holding the printed output must be devised.

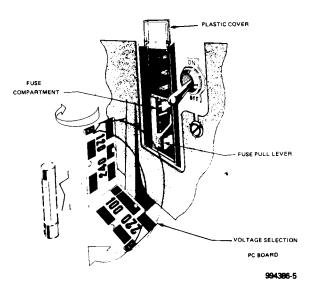

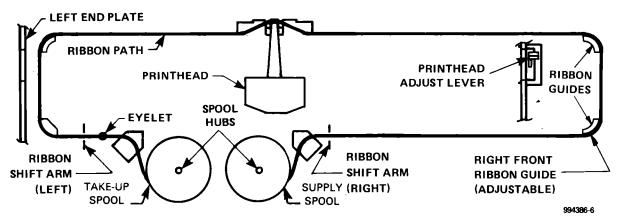

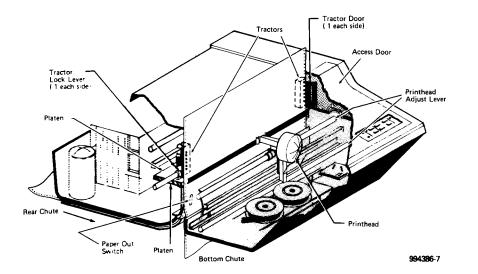

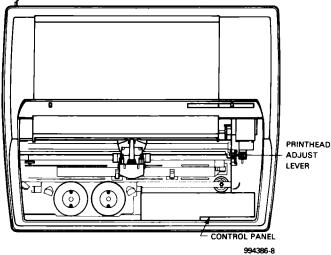

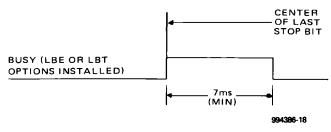

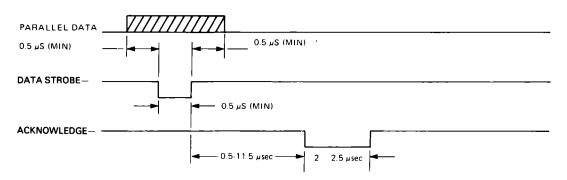

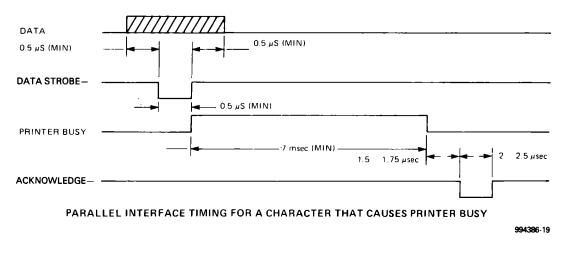

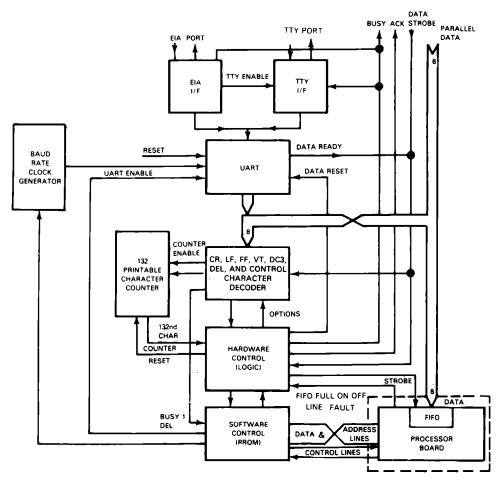

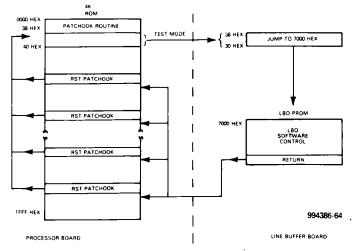

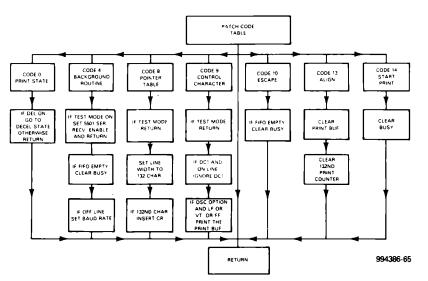

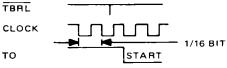

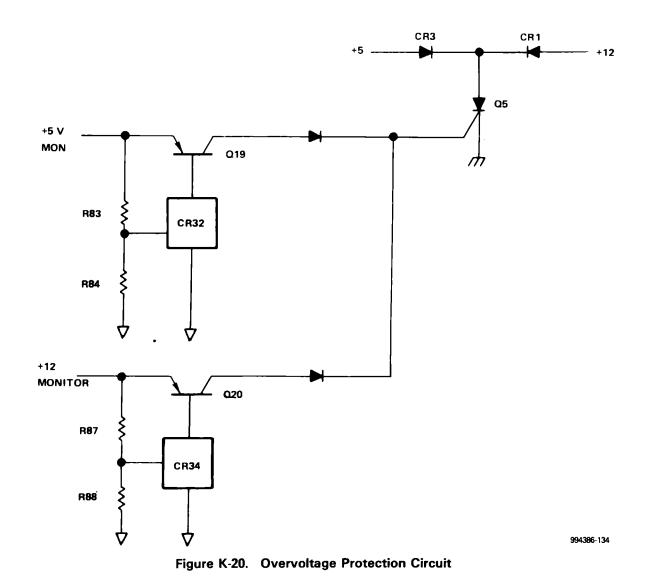

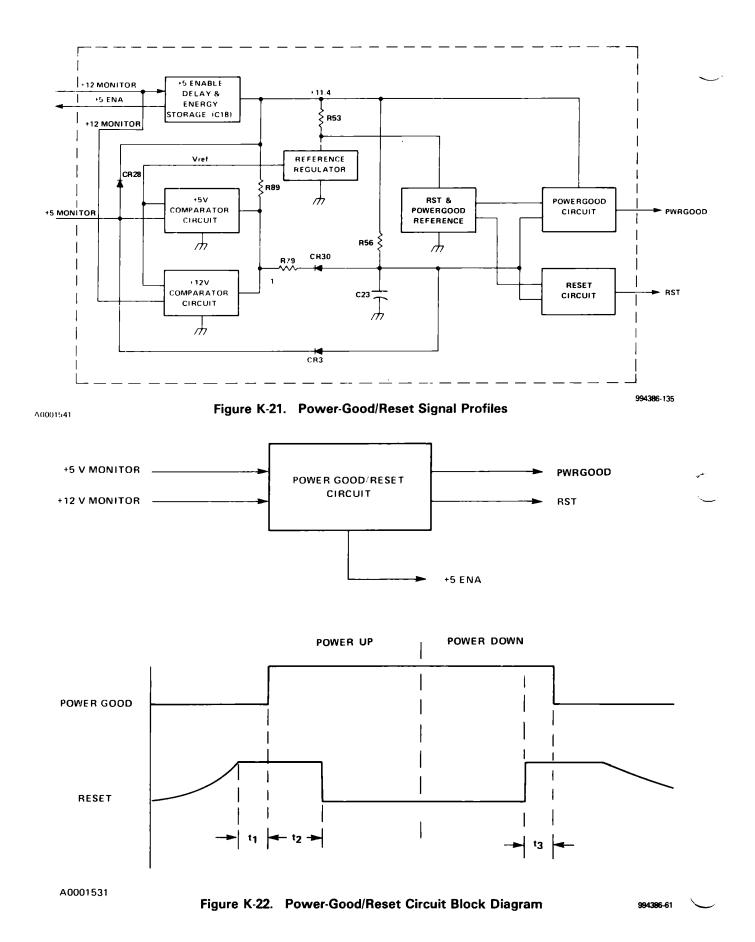

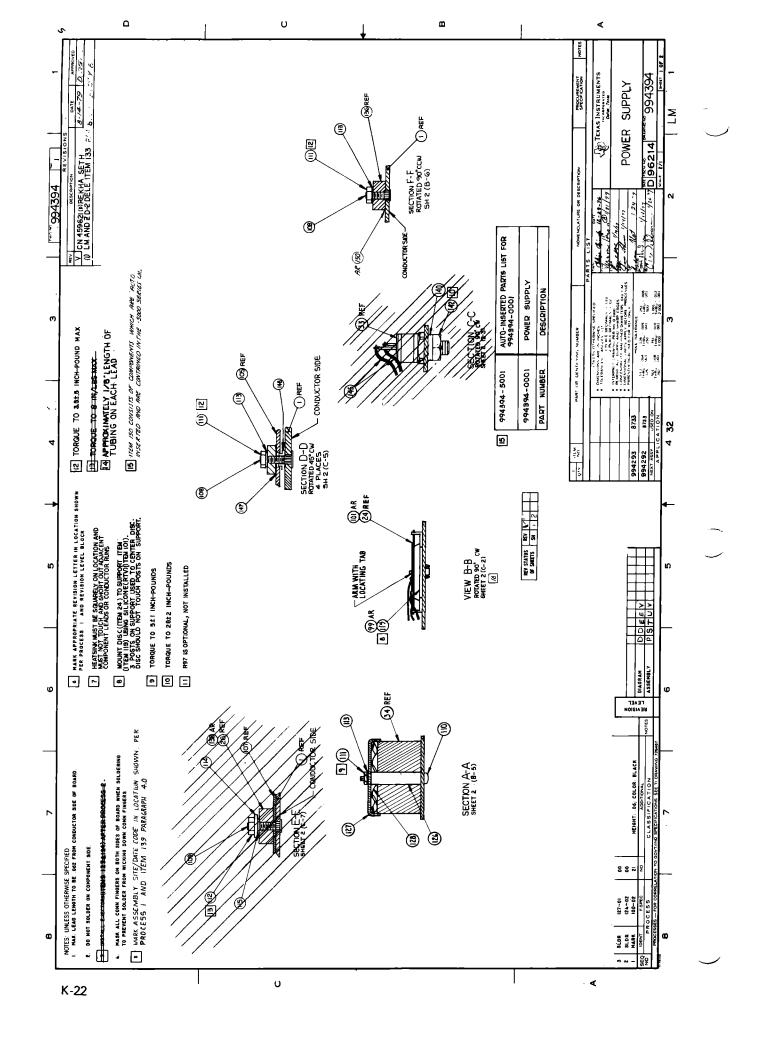

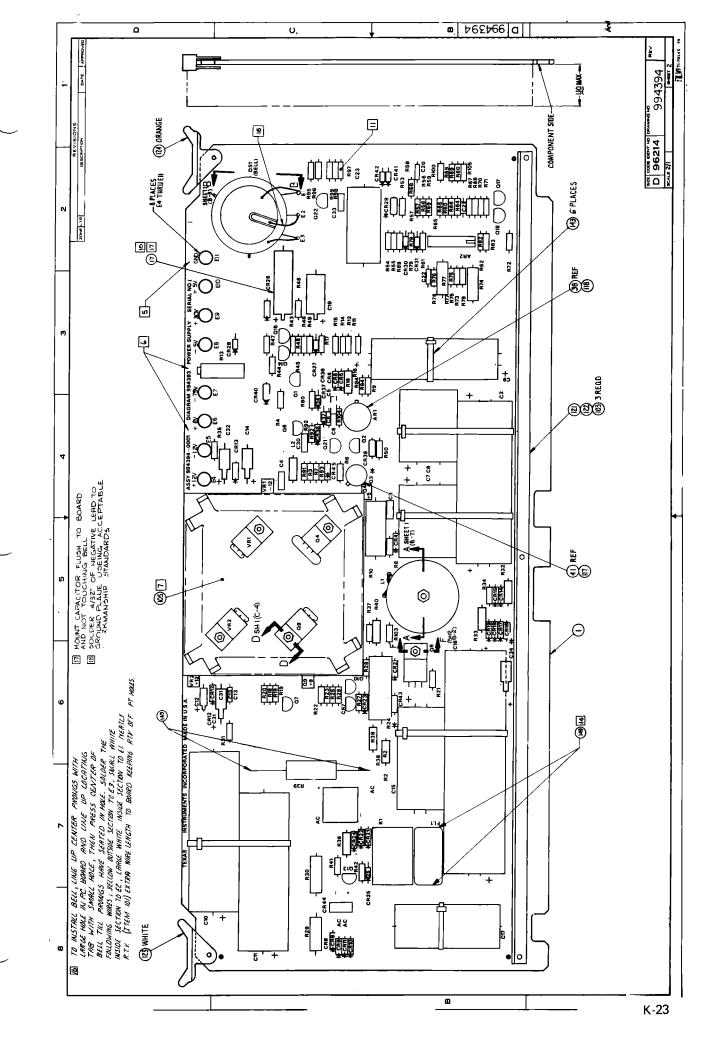

Besides the correct support, a necessary consideration is to provide adequate ventilation. The printer requires approximately 50 mm (2 in.) for proper ventilation. Particular attention should be paid to ensure that the sides which contain both the intake fans and exhaust louvers are clear.